Chapter 3: GIC 分区

-

本章描述 GIC 逻辑分区。包含以下部分: • GIC 逻辑组件 。

-

中断旁路支持 。

3.1 GIC 逻辑组件

GICv3 架构由一组逻辑组件组成:

-

一个 Distributor 。

-

每个支持的 PE 的一个 Redistributor。

-

每个支持的 PE 的一个 CPU interface。

-

Interrupt Translation Service 组件(ITS),支持事件到 LPI 的可选转换。

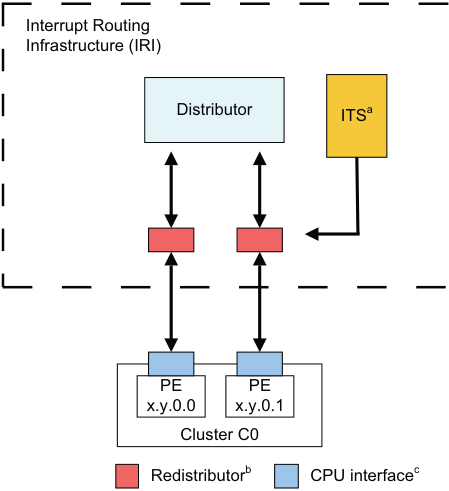

Distributor、Redistributor 和 ITS 统称为 IRI。

图 3-1 显示了 IRI。

图像文本

Interrupt Routing

Infrastructure (IRI)

Distributor ITS [a]

PE PE

x.y.0.0 x.y.0.1

Cluster C0

Redistributor [b] CPU interface [c]

b. 每个 PE 有一个 Redistributor。c. 每个 PE 有一个 CPU interface。

图 3-1 中断路由基础设施 CPU interface 处理所有已实现异常级别的物理中断:

-

转换为 LPI 的中断可选择通过 ITS 路由到 Redistributor 和 CPU interface。

-

PPI 直接从源路由到本地 Redistributor。

-

SPI 从源通过 Distributor 路由到目标 Redistributor 和关联的 CPU interface。

-

SGI 由软件通过 CPU interface 和 Redistributor 生成。然后通过 Distributor 路由到一个或多个目标 Redistributor 和关联的 CPU interface。

在 GICv3 中,ITS 是可选组件,将事件转换为物理 LPI。该架构还支持不需要使用 ITS 的直接 LPI。当支持 LPI 时,IMPLEMENTATION DEFINED 是否支持以下任一种:

-

通过访问 Redistributor 中的寄存器支持直接 LPI。

-

通过 ITS 提供 LPI 支持。

实现必须仅支持这些方法中的一种。

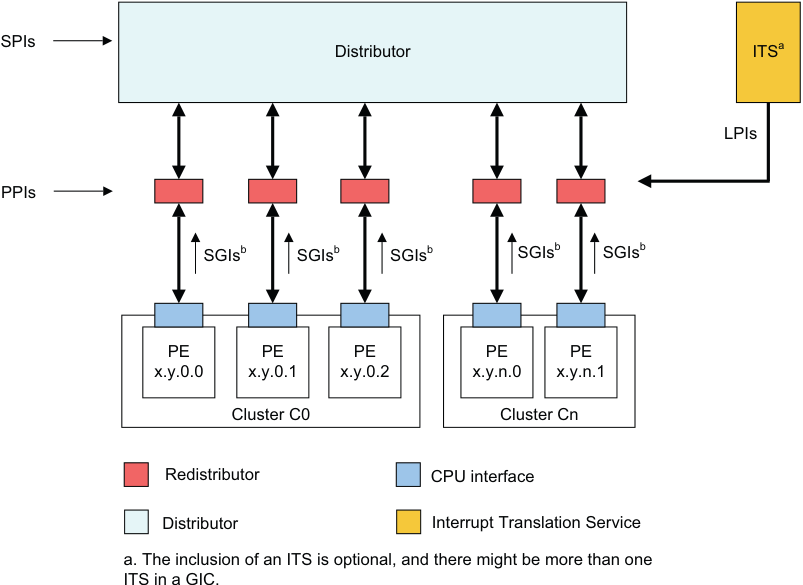

在 GICv4 中,必须包含至少一个 ITS 来提供对虚拟 LPI 直接注入的支持。 图 3-2 显示了包含 ITS 的实现中的 GIC 分区。

图像文本

SPIs

Distributor ITS [a]

LPIs

PPIs

SGIs [b] SGIs [b] SGIs [b] SGIs [b] SGIs [b]

PE PE PE PE PE

x.y.0.0 x.y.0.1 x.y.0.2 x.y.n.0 x.y.n.1

Cluster C0 Cluster Cn

Redistributor CPU interface

Distributor Interrupt Translation Service

a. ITS 的包含是可选的,一个 GIC 中可能有多个

ITS。

图 3-2 带有 ITS 的 GIC 逻辑分区

ITS 和 Redistributor 之间的通信机制是 IMPLEMENTATION DEFINED。

CPU interface 和 Redistributor 之间的通信机制也是 IMPLEMENTATION DEFINED。

注意 Arm 建议实现使用 GIC Stream 协议在 CPU interface 和 Redistributor 之间通信,请参见附录 A GIC Stream 协议接口 。

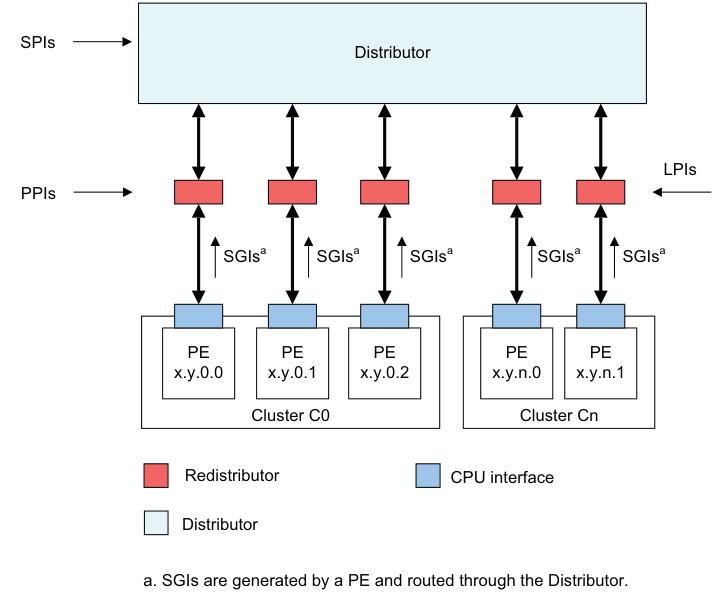

图 3-3 显示了不包含 ITS 且支持直接 LPI 的实现中的 GIC 分区。 3.1 GIC 逻辑组件

图像文本

SPIs

Distributor

LPIs

PPIs

SGIs [a] SGIs [a] SGIs [a] SGIs [a] SGIs [a]

PE PE PE PE PE

x.y.0.0 x.y.0.1 x.y.0.2 x.y.n.0 x.y.n.1

Cluster C0 Cluster Cn

Redistributor CPU interface

Distributor

a. SGI 由 PE 生成并通过 Distributor 路由。

以下列表更详细地描述了图 3-2 中描绘的组件:

Distributor

Distributor 对 SPI 和 SGI 进行中断优先级排序和分发到连接到系统中 PE 的 Redistributor 和 CPU interface。GICD_CTLR 提供以下全局设置:

-

启用亲和性路由。

-

禁用安全性。

-

启用 Secure 和 Non-secure Group 1 中断。

-

启用 Group 0 中断。

对于 SPI,Distributor 提供编程接口用于:

-

启用或禁用 SPI。

-

设置每个 SPI 的优先级。

-

每个 SPI 的路由信息。

-

将每个 SPI 设置为电平敏感或边沿触发。

-

生成基于消息的 SPI。

-

将每个 SPI 分配给中断组。

-

控制 SPI 的待处理和活动状态。

Distributor 寄存器以 GICD_ 前缀标识。

有关更多信息,请参见第 2 章 中断分发和路由 。

注意 在传统操作期间处理物理中断时,Distributor 控制 PPI 和 SGI 的配置信息。请参见第 14 章 传统操作和非对称配置 。

中断转换服务,ITS

ITS 是 GICv3 架构中的可选硬件机制,将 LPI 路由到适当的 Redistributor。软件使用命令队列配置 ITS。与 ITS 关联的内存中的表结构将与设备关联的 EventID 转换为 PE 的待处理 INTID。

ITS 在 GICv4 中不是可选的,所有 GICv4 实现必须包含至少一个 ITS。

有关更多信息,请参见 中断转换服务 。

Redistributor Redistributor 是连接到 PE 的 CPU interface 的 IRI 部分。Redistributor 使用内存中保存的数据结构保存所有物理 LPI 的控制、优先级和待处理信息。Redistributor 中的两个寄存器指向这些数据结构:

-

GICR_PROPBASER。

-

GICR_PENDBASER。

在 GICv4 中,Redistributor 还包含寄存器来处理由 ITS 转发到 Redistributor 并直接转发到 VM 的虚拟 LPI,而无需涉及 hypervisor。这被称为虚拟中断的 直接注入 到 VM。

在 GICv4 中,Redistributor 共同托管所有虚拟 LPI 的控制、优先级和待处理信息,使用内存中保存的数据结构。Redistributor 中的两个寄存器指向这些数据结构:

-

GICR_VPROPBASER。

-

GICR_VPENDBASER。

在支持 LPI 但不包含 ITS 的实现中,GICR_* 寄存器包含简单的内存映射接口来信号和控制物理 LPI。

Redistributor 提供编程接口用于:

-

识别、控制和配置支持的功能以启用中断和实现的中断路由。

-

启用或禁用 SGI 和 PPI。

-

设置 SGI 和 PPI 的优先级。

-

将每个 PPI 设置为电平敏感或边沿触发。

-

将每个 SGI 和 PPI 分配给中断组。

-

控制 SGI 和 PPI 的待处理状态。

-

控制 SGI 和 PPI 的活动状态。

-

连接的 PE 的电源管理支持。

-

当支持 LPI 时,支持关联中断属性及其待处理状态的内存中数据结构的基地址控制。

-

当支持 GICv4 时,支持关联虚拟中断属性及其待处理状态的内存中数据结构的基地址控制。

Redistributor 寄存器以 GICR_ 前缀标识。

有关 Redistributor 的更多信息,请参见 亲和性路由 和 Distributor 和 Redistributor 。

CPU interface

GIC 架构支持向系统中的 PE 提供寄存器接口的 CPU interface。每个 CPU interface 提供编程接口用于:

-

通用控制和配置,根据实现的安全状态和传统支持要求启用中断处理。

-

确认中断。

-

执行优先级下降。

-

中断的停用。

-

为 PE 设置中断优先级掩码。

-

为 PE 定义抢占策略。

-

确定 PE 的最高优先级待处理中断。

CPU interface 有几个组件:

-

允许监管级别软件控制物理中断处理的组件。与此关联的寄存器以 ICC_ 前缀标识。

-

允许监管级别软件控制虚拟中断处理的组件。与此关联的寄存器以 ICV_ 前缀标识。

-

允许 hypervisor 控制待处理中断集的组件。与此关联的寄存器以 ICH_ 前缀标识。

注意 CPU interface 中的系统寄存器与处理物理域中中断的软件相关联,或与作为 VM 一部分在 Non-secure EL1 执行相关联。HCR_EL2 的配置确定访问是针对物理资源还是虚拟资源。

在 EL2 访问的用于控制 PE 的活动、待处理以及活动和待处理虚拟中断列表的系统寄存器以 ICH_ 前缀标识。

有关处理物理中断的更多信息,请参见第 4 章 物理中断处理和优先级 。

有关处理虚拟中断的更多信息,请参见第 6 章 虚拟中断处理和优先级 。

3.2 中断旁路支持

CPU interface 可选择包含中断信号旁路,以便当接口的中断信号被禁用时,传统中断信号传递到 PE 上的中断请求输入,绕过 GIC 功能。

是否支持旁路是 IMPLEMENTATION DEFINED。

确定是否使用 GICv3 FIQ 和 IRQ 输出或旁路信号的控制因是否启用系统寄存器访问而异。

当启用系统寄存器访问时,在最高实现异常级别使用 ICC_SRE_EL1、ICC_SRE_EL2 或 ICC_SRE_EL3 中的两个位来控制旁路禁用,视情况而定:

-

对于 FIQ 旁路,这是 DFB 位。

-

对于 IRQ 旁路,这是 DIB 位。

当启用系统寄存器访问时使用此旁路机制。有关传统操作期间旁路支持的信息,请参见 传统操作和旁路支持 。

GIC 支持的中断组分配给 FIQ 和 IRQ,如 中断分组 中所述。当启用旁路时,必须在 CPU interface 禁用中断组,否则 GICv3 实现的行为是 UNPREDICTABLE。这意味着:

-

当 ICC_SRE_ELx.DFB == 0 时,ICC_IGRPEN0_EL1.Enable 必须为 0。

-

当 ICC_SRE_ELx.DIB == 0 时,ICC_IGRPEN1_EL1.Enable 必须为 0。

有关启用中断的更多信息,请参见 启用中断分发 。

有关未启用系统寄存器访问时行为的信息,请参见第 14 章 传统操作和非对称配置 。

对于 FIQ,以下伪代码确定向 PE 发送中断信号的源。

if ICC_SRE_EL3.SRE == 1 then

if ICC_SRE_EL3.DFB == 0 then

if ICC_SRE_EL1.SRE Secure == 1 then

BypassFIQsource

else

use legacy bypass support

else

use GICv3 FIQ output

else

use legacy bypass support

对于 IRQ,以下伪代码确定向 PE 发送中断信号的源。

if ICC_SRE_EL3.SRE == 1 then

if ICC_SRE_EL3.DIB == 0 then

if ICC_SRE_EL1.SRE Secure == 1 then

BypassIRQsource

else

use legacy bypass support

else

use GICv3 IRQ output

else

use legacy bypass support