前言

Arm® Generic Interrupt Controller Architecture Specification GIC 架构版本 3 和版本 4

Copyright © 2008, 2011, 2015-2021 Arm Limited or its affiliates. All rights reserved.

Arm Generic Interrupt Controller Architecture Specification GIC 架构版本 3 和版本 4

Copyright © 2008, 2011, 2015-2021 Arm Limited or its affiliates. All rights reserved.

版本信息

本文档进行了以下更改。

变更历史

| 日期 | 版本 | 保密性 | 变更 |

|---|---|---|---|

| June 2015 | A | Non-confidential | GICv3 和 GICv4 版本 A 首次发布。 |

| December 2015 | B | Non-confidential | GICv3 和 GICv4 版本 B 首次发布。 |

| July 2016 | C | Non-confidential | GICv3 和 GICv4 版本 C 首次发布。 |

| August 2017 | D | Non-confidential | GICv3 和 GICv4 版本 D 首次发布。 |

| January 2019 | E | Non-confidential | GICv3 和 GICv4 版本 E 首次发布。 |

| February 2020 | F | Non-confidential | GICv3 和 GICv4.1 版本 F 首次发布。 |

| February 2021 | G | Non-confidential | GICv3 和 GICv4.1 版本 G 首次发布。 |

本规范中的部分信息先前发布于 Arm[®] Generic Interrupt Controller, Architecture version 2.0, Architecture Specification 。

专有声明

本文档受版权和其他相关权利保护,本文档中包含的信息的实践或实施可能受一项或多项专利或待审专利申请的保护。未经 ARM 事先明确书面许可,不得以任何形式通过任何方式复制本文档的任何部分。除非明确规定,否则本文档不授予任何知识产权的明示或暗示许可、禁反言或其他形式的许可。

您对本文档中信息的访问,以您接受不会使用或允许他人使用这些信息来确定实施是否侵犯任何第三方专利为条件。

本文档按“现状“提供。ARM 不提供任何明示、暗示或法定的陈述和保证,包括但不限于关于本文档的适销性、满意质量、不侵权或特定用途适用性的暗示保证。为避免疑义,ARM 不对专利、版权、商业秘密或其他权利的范围和内容进行任何陈述,也未进行任何分析来识别或理解其范围和内容。

本文档可能包含技术错误或印刷错误。

在法律不禁止的范围内,无论何种情况下,ARM 均不对任何损害承担责任,包括但不限于任何直接、间接、特殊、偶然、惩罚性或后果性损害,无论如何造成,无论何种责任理论,因使用本文档而产生,即使 ARM 已被告知可能发生此类损害。

本文档仅包含商业项目。您应负责确保任何使用、复制或披露本文档完全符合任何相关出口法律法规,以确保本文档或其任何部分不会直接或间接违反此类出口法律而出口。在提及 ARM 客户时使用“合作伙伴“一词,并不打算创建或指代与任何其他公司的任何合作伙伴关系。ARM 可能随时对本文档进行更改,恕不另行通知。

如果这些条款中包含的任何条款与涵盖本文档与 ARM 的任何点击或签署书面协议的任何条款冲突,则点击或签署的书面协议优于并取代这些条款的冲突条款。本文档可能为方便起见翻译成其他语言,您同意如果本文档的英文版本与任何翻译之间存在任何冲突,协议英文版本的条款应占上风。

ARM 公司徽标和标有 ® 或 ™ 的词语是 ARM Limited(或其子公司)在美国和/或其他地方的注册商标或商标。保留所有权利。本文档中提及的其他品牌和名称可能是其各自所有者的商标。请遵循 ARM 的商标使用指南:http://www.arm.com/company/policies/trademarks。 Copyright © 2008, 2011, 2015-2021 Arm Limited or its affiliates. All rights reserved.

Arm Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

LES-PRE-20349

保密状态

本文档是非保密的。使用、复制和披露本文档的权利可能受到根据 Arm 与 Arm 交付本文档的一方签订的协议条款的许可限制。

产品状态

本文档中的信息是最终的,即用于已开发的产品。

网址

http://www.arm.com

渐进术语承诺

Arm 重视包容性社区。Arm 认识到我们和我们的行业使用了可能令人反感的术语。Arm 努力引领行业并创造变革。

本文档的先前版本包含可能令人反感的术语。我们已替换这些术语。

如果您在本文档中发现令人反感的术语,请联系 terms@arm.com。

目录 Arm Generic Interrupt Controller Architecture Specification GIC 架构版本 3 和版本 4

| 前言 | |||

|---|---|---|---|

| 关于本规范 | |||

| 使用本规范 | |||

| 约定 | |||

| 补充阅读 | |||

| 反馈 | |||

| 第 | 1 | 章 | 介绍 |

| — | — | — | — |

| 1.1 | 关于 Generic Interrupt Controller (GIC) | ||

| 1.2 | 术语 | ||

| 1.3 | 支持的配置和兼容性 | ||

| 第 | 2 | 章 | 中断的分发和路由 |

| 2.1 | Distributor 和 Redistributor | ||

| 2.2 | INTID | ||

| 2.3 | 亲和性路由 | ||

| 第 | 3 | 章 | GIC 分区 |

| 3.1 | GIC 逻辑组件 | ||

| 3.2 | 中断旁路支持 | ||

| 第 | 4 | 章 | 物理中断处理和优先级排序 |

| 4.1 | 中断生命周期 | ||

| 4.2 | Locality-specific Peripheral Interrupt | ||

| 4.3 | Private Peripheral Interrupt | ||

| 4.4 | Software Generated Interrupt | ||

| 4.5 | Shared Peripheral Interrupt | ||

| 4.6 | 中断分组 | ||

| 4.7 | 启用中断分发 | ||

| 4.8 | 中断优先级排序 | ||

| 第 | 5 | 章 | Locality-specific Peripheral Interrupt 和 ITS |

| 5.1 | LPI | ||

| 5.2 | Interrupt Translation Service | ||

| 5.3 | ITS 命令 | ||

| 5.4 | 通用 ITS 伪代码函数 | ||

| 5.5 | ITS 命令错误编码 | ||

| 5.6 | ITS 电源管理 | ||

| 第 | 6 | 章 | 虚拟中断处理和优先级排序 |

| 6.1 | 关于 GIC 对虚拟化的支持 | ||

| 6.2 | 操作概述 | ||

| 6.3 | VM 的配置和控制 | ||

| 6.4 | 伪代码 | ||

| 第 | 7 | 章 | GICv4.0 虚拟 LPI 支持 |

| 7.1 | 关于 GICv4.0 虚拟 Locality-specific Peripheral Interrupt 支持 | ||

| 7.2 | 虚拟中断的直接注入 | ||

| 第 | 8 | 章 | GICv4.1 虚拟中断支持 |

| 8.1 | 关于 GICv4.1 虚拟中断支持 | ||

| 8.2 | CPU interface 的变更 | ||

| 8.3 | ITS 命令 | ||

| 8.4 | vPEID 宽度 | ||

| 8.5 | 门铃 | ||

| 8.6 | vPE 驻留和定位数据结构 | ||

| 8.7 | 基于寄存器的 vLPI 失效 | ||

| 8.8 | vSGI 的直接注入 | ||

| 第 | 9 | 章 | 内存分区和监控 |

| 9.1 | 概述 | ||

| 9.2 | MPAM 和 Redistributor | ||

| 9.3 | MPAM 和 ITS | ||

| 9.4 | GIC 对 MPAM 的使用 | ||

| 9.5 | GICv4.1 数据结构和 MPAM | ||

| 第 | 10 | 章 | 连接到 Armv8-R AArch64 PE |

| 10.1 | Armv8-R AArch64 CPU interface 要求 | ||

| 第 | 11 | 章 | 电源管理 |

| 11.1 | 电源管理 | ||

| 第 | 12 | 章 | 程序员模型 |

| 12.1 | 关于程序员模型 | ||

| 12.2 | AArch64 系统寄存器描述 | ||

| 12.3 | 虚拟寄存器的 AArch64 系统寄存器描述 | ||

| 12.4 | AArch64 虚拟化控制系统寄存器 | ||

| 12.5 | AArch32 系统寄存器描述 | ||

| 12.6 | 虚拟寄存器的 AArch32 系统寄存器描述 | ||

| 12.7 | AArch32 虚拟化控制系统寄存器 | ||

| 12.8 | GIC Distributor 寄存器映射 | ||

| 12.9 | GIC Distributor 寄存器描述 | ||

| 12.10 | GIC Redistributor 寄存器映射 | ||

| 12.11 | GIC Redistributor 寄存器描述 | ||

| 12.12 | GIC CPU interface 寄存器映射 | ||

| 12.13 | GIC CPU interface 寄存器描述 | ||

| 12.14 | GIC 虚拟 CPU interface 寄存器映射 | ||

| 12.15 | GIC 虚拟 CPU interface 寄存器描述 | ||

| 12.16 | GIC 虚拟接口控制寄存器映射 | ||

| 12.17 | GIC 虚拟接口控制寄存器描述 | ||

| 12.18 | ITS 寄存器映射 | ||

| 12.19 | ITS 寄存器描述 | ||

| 12.20 | 伪代码 | ||

| 第 | 13 | 章 | 系统错误报告 |

| 13.1 | 关于系统错误报告 | ||

| 第 | 14 | 章 | 传统操作和非对称配置 |

| 14.1 | 中断和非对称配置的传统支持 | ||

| 14.2 | 非对称配置 | ||

| 14.3 | VM 传统操作的支持 | ||

| 附录 A | GIC Stream 协议接口 | ||

| A.1 | 概述 | ||

| A.2 | 信号和 GIC Stream 协议 | ||

| A.3 | GIC Stream 协议 | ||

| A.4 | 命令和响应包格式的字母表列表 | ||

| 附录 B | 伪代码定义 | ||

| B.1 | 关于 Arm 伪代码 | ||

| B.2 | 数据类型 | ||

| B.3 | 表达式 | ||

| B.4 | 操作符和内置函数 | ||

| B.5 | 语句和程序结构 | ||

| B.6 | 伪代码术语 | ||

| B.7 | 杂项辅助程序和支持函数 |

词汇表

vii viii

前言

本前言介绍 Arm[®] Generic Interrupt Controller Architecture Specification 。包含以下部分:

-

关于本规范 第 x 页。

-

使用本规范 第 xi 页。

-

约定 第 xiii 页。

-

补充阅读 第 xiv 页。

-

反馈 第 xv 页。 前言 关于本规范

关于本规范

本规范描述了 Arm Generic Interrupt Controller (GIC) 架构。它定义了 GIC 架构的版本 3.0、3.1、3.2(GICv3)、4.0 和 4.1(GICv4)。

在整个文档中,对 GIC 或 一个 GIC 的引用指实现 GIC 架构的设备。除非上下文明确表示引用是设备的 IMPLEMENTATION DEFINED 功能,否则这些引用描述本规范的要求。

目标受众

本规范适用于想要在一系列符合 Arm 标准的实现中设计、实现或编程 GIC 的用户,从简单的单处理器实现到复杂的多处理器系统。它不假设熟悉 GIC 的先前版本。

本规范假设用户对 Arm 产品有一定经验,并熟悉描述 Armv8 架构的术语。有关更多信息,请参见 Arm[®] Architecture Reference Manual, Armv8, for Armv8-A architecture profile 。 前言 使用本规范

使用本规范

本规范组织为以下章节:

第 1 章 介绍

阅读本章了解 GIC 的概述,以及本文档使用的术语信息。

第 2 章 中断的分发和路由

阅读本章了解 GIC 如何使用亲和性路由分发中断。

第 3 章 GIC 分区

阅读本章了解 GIC 分区的概述和 GIC 逻辑组件的信息。 第 4 章 物理中断处理和优先级排序 阅读本章了解 GIC 如何处理物理中断。 第 5 章 Locality-specific Peripheral Interrupt 和 ITS 阅读本章了解 Locality-specific Peripheral Interrupt (LPI) 和 Interrupt Translation Service (ITS) 的使用描述。 第 6 章 虚拟中断处理和优先级排序 阅读本章了解 GIC 如何处理虚拟中断。 第 7 章 GICv4.0 虚拟 LPI 支持

阅读本章了解 GIC 如何处理虚拟中断。 第 8 章 GICv4.1 虚拟中断支持 阅读本章了解 GICv4.1 中虚拟中断支持的变更。 第 9 章 内存分区和监控 阅读本章了解 GIC 上下文中的内存分区和监控描述。 第 10 章 连接到 Armv8-R AArch64 PE 阅读本章了解将 GIC 连接到实现 Armv8-R64 的 PE。 第 11 章 电源管理 阅读本章了解 GIC 电源管理。 第 12 章 程序员模型 阅读本章了解 GIC 寄存器接口和所有 GIC 寄存器的描述。 第 13 章 系统错误报告 阅读本章了解 GIC 对错误报告的支持。 第 14 章 传统操作和非对称配置 阅读本章了解 GIC 对传统操作和非对称配置的支持。 附录 A GIC Stream 协议接口

阅读此附录了解 GIC Stream 协议接口使用的 AXI4-Stream 协议标准基于消息的接口描述。

附录 B 伪代码定义

阅读此附录了解本规范中使用的伪代码定义。

词汇表

阅读词汇表了解本规范中使用的一些术语定义。 前言 使用本规范

前言 约定

约定

以下部分描述本书可能使用的约定:

-

排版约定 。

-

信号 。

-

数字 。

-

伪代码描述 。

排版约定

排版约定为:

斜体 引入特殊术语,表示引用。 粗体 表示信号名称,在适当时用于描述性列表中的术语。 等宽字体 用于汇编语法描述、伪代码和源代码示例。也在正文中用于指令助记符和对汇编语法描述、伪代码和源代码示例中出现的其他项的引用。

小型大写字母

用于具有特定技术含义且包含在 词汇表 中的少数术语。

彩色文本 表示链接。这可以是:

-

URL,例如 https://developer.arm.com。

-

交叉引用,如果引用信息不在当前页面,则包括引用信息的页码,例如,关于 Generic Interrupt Controller (GIC) 第 1-18 页。

-

链接,指向章节或附录、词汇表条目,或定义彩色术语的文档部分,例如,Banked register 或 GICC_CTLR。

信号

一般来说,本规范不定义处理器信号,但它包含一些信号示例和建议。信号约定为:

信号电平 断言信号的电平取决于信号是高电平有效还是低电平有效。断言意味着:

-

高电平有效信号为 HIGH

-

低电平有效信号为 LOW。

小写 n 在信号名称的开头或结尾表示低电平有效信号。

数字

数字通常用十进制书写。二进制数字前加 0b,十六进制数字前加 0x。在这两种情况下,前缀和相关值都用等宽字体书写,例如 0xFFFF0000。

伪代码描述

本规范使用一种形式的伪代码来提供指定功能的精确描述。此伪代码用等宽字体书写,并遵循 Arm[®] Architecture Reference Manual, Armv8, for Armv8-A architecture profile 和 Arm[®] Architecture Reference Manual, Armv7-A and Armv7-R edition 中描述的约定。 前言 补充阅读

补充阅读

本节列出了 Arm 和第三方的相关出版物。

请参见 Arm Developer,https://developer.arm.com 获取 Arm 文档。

Arm 出版物

-

AMBA[®] 4 AXI4-Stream Protocol Specification (ARM IHI 0051)。

-

Arm[®] Architecture Reference Manual, Armv7-A and Armv7-R edition (ARM DDI 0406)。

-

Arm[®] Architecture Reference Manual, Armv8, for Armv8-A architecture profile (ARM DDI 0487)。

-

Arm[®] Architecture Reference Manual Supplement, Memory System Resource Partitioning and Monitoring (MPAM), for Armv8-A (ARM DDI 0598)。

-

Arm[®] Generic Interrupt Controller, Architecture version 2.0, Architecture Specification (ARM IHI 0048)。

-

Arm[®] CoreSight[™] Architecture Specification v3.0 (ARM IHI 0029)。

-

Arm[®] Server Base System Architecture (SBSA) (ARM-DEN-0029)。

-

GICv3 and GICv4 Software Overview (DAI 0492)。

-

• Application Note GIC Stream Protocol Interface (ARM-ECM-0495013)。

其他出版物

本手册中引用或提供更多信息的以下书籍:

- JEDEC Solid State Technology Association, Standard Manufacture’s Identification Code , JEP106。 前言 反馈

反馈

Arm 欢迎对其文档提供反馈。

对本手册的反馈

-

如果您对本手册的内容有意见,请发送电子邮件至 errata@arm.com。请提供: • 标题。

-

编号,Arm IHI 0069G。

-

您的意见适用的页码。

-

您意见的简明解释。

Arm 也欢迎对新增和改进的一般建议。 前言 反馈

Chapter 1: 简介

本章提供了GIC架构的简介。它提供了GIC架构的概述以及该架构中的新特性。还提供了本文档使用的术语定义。包含以下部分:

-

关于Generic Interrupt Controller (GIC) .

-

术语 .

-

支持的配置和兼容性 . 1.1 关于Generic Interrupt Controller (GIC)

1.1 关于Generic Interrupt Controller (GIC)

GICv3架构被设计用来与Armv8-A和Armv8-R兼容的_处理单元_ ,PE配合工作。

Generic Interrupt Controller (GIC)架构定义:

-

对任何连接到GIC的PE处理所有中断源的架构要求。

-

适用于单处理器或多处理器系统的通用中断控制器编程接口。

GIC是支持和控制中断的架构化资源。它提供:

-

用于管理中断源、中断行为以及中断路由到一个或多个PE的寄存器。

-

支持:

- Armv8架构。

-

Locality-specific Peripheral Interrupts (LPI)。

- Private Peripheral Interrupts (PPI)。

-

Software Generated Interrupts (SGI)。

-

Shared Peripheral Interrupts (SPI)。

-

中断屏蔽和优先级处理。

-

单处理器和多处理器系统。

-

-

电源管理环境中的唤醒事件。

对于每个PE,GIC架构描述了如何从系统内不同类型的中断生成IRQ和FIQ中断。Armv8-A异常模型描述了PE如何处理这些IRQ和FIQ中断。

中断处理也依赖于Armv8架构的其他方面,如安全状态和虚拟化支持。Arm架构提供了两种安全状态,每种都有相关的物理内存地址空间:

-

安全状态。

-

非安全状态。

GIC架构支持与两种安全状态相关的中断路由和处理。有关更多信息,请参阅_中断分组和安全性_。

GIC架构支持与_虚拟机_,VM相关的虚拟中断处理的Armv8模型。虚拟化系统有:

-

一个管理程序必须包含在EL2执行的组件,负责在VM之间进行切换。

-

在EL1执行的多个VM。

-

在VM上的EL0执行的应用程序。

有关Armv8架构的更多信息,请参阅_Arm[®] Architecture Reference Manual, Armv8, for Armv8-A architecture profile_。有关VM的更多信息,请参阅_关于GIC虚拟化支持_。

本规范定义了GIC架构的版本3.0、版本3.1、版本3.2(统称为GICv3)、版本4.0和版本4.1(统称为GICv4.1)。版本2.0(GICv2)仅在GICv3可选的传统操作支持方面进行描述,请参阅_具有传统操作的GICv3_。有关GICv2架构的详细信息,请参阅_Arm[®] Generic Interrupt Controller, Architecture version 2.0, Architecture Specification_。

注意 由于GICv4是GICv3.0和GICv3.1的扩展,本手册中对GICv3的所有引用同样适用于GICv4,除非明确另有说明。GICv4.1架构规范的任何变更都会相应地标出。

1.1.1 从GICv2开始的GIC架构变更

GIC可扩展性

GICv2架构只支持最多八个PE,因此具有无法扩展到大型系统的功能。GICv3通过改变中断路由的机制(称为_亲和性路由_)以及在中断分发中引入一个新组件(称为_Redistributor_)来解决这个问题。有关更多信息,请参阅第3章_GIC分区_。

通过将GICD_CTLR.ARE_S或GICD_CTLR.ARE_NS设置为1来启用安全状态的亲和性路由。

中断分组

_中断分组_是GICv3用来将中断处理与Armv8异常模型对齐的机制:

-

Group 0物理中断预期在最高实现的异常级别处理。

-

Secure Group 1物理中断预期在Secure EL1或EL2处理。

-

Non-secure Group 1物理中断在使用虚拟化的系统中预期在Non-secure EL2处理,或在不使用虚拟化的系统中在Non-secure EL1处理。

这些中断组可以映射到Armv8 FIQ和IRQ信号上,如_中断分组_中所述,使用来自Armv8架构和GICv3架构内的配置位。

在GICv3中,中断分组支持:

-

将每个中断配置为Group 0、Secure Group 1或Non-secure Group 1。

-

使用FIQ异常请求向目标PE发送Group 0物理中断信号。

-

以允许它们在自己的安全状态下使用IRQ处理程序进行处理的方式向目标PE发送Group 1物理中断信号。Group 1中断的确切处理取决于当前的异常级别和安全状态,如第4章_物理中断处理和优先级_中所述。

-

Group 0和Group 1中断优先级处理的统一方案。

Interrupt Translation Service (ITS)

Interrupt Translation Service,ITS,提供了允许软件控制如何将转发到ITS的中断转换为:

-

物理中断,在GICv3和GICv4中。

-

虚拟中断,仅在GICv4中。

ITS还允许软件确定转换后中断的目标Redistributor。软件可以通过命令接口和内存中相关的基于表的结构控制ITS。Interrupt Translation Service (ITS)的输出总是LPI,这是一种基于消息的中断形式。请参阅_Interrupt Translation Service_。

Locality-specific Peripheral Interrupts (LPI)

LPI是一类新的中断,显著扩展了GIC可以处理的中断ID空间。LPI是可选的,如果实现,可以由Interrupt Translation Service,ITS生成和支持。请参阅_LPI_。

Software Generated Interrupts (SGI)

由于GICv3支持大规模系统的能力,SGI的上下文已修改,不再包含源PE的身份。请参阅_Software Generated Interrupts_。

注意

原始的SGI格式仅在支持传统操作的GIC实现中可用。

Shared Peripheral Interrupts (SPI)

Distributor中添加了一组新寄存器,以支持基于消息的SPI的设置和清除。请参阅_Shared Peripheral Interrupts_。

System register接口

该接口在Armv8-A或Armv8-R PE中使用System register指令,为CPU interface寄存器提供紧密耦合的接口。该接口用于与中断处理和优先级掩码直接相关的寄存器,以最小化访问延迟。对于虚拟化,以这种方式访问的寄存器包括VM中断处理程序访问的寄存器,以及将虚拟中断从管理程序转发到VM的寄存器。所有其他寄存器都是内存映射的。

对于AArch64状态,System register接口的访问由以下设置启用:

-

ICC_SRE_EL1.SRE == 1。

-

• ICC_SRE_EL2.SRE == 1。 • ICC_SRE_EL3.SRE == 1。

对于AArch32状态,System register接口的访问由以下设置启用:• ICC_SRE.SRE == 1。 • ICC_HSRE.SRE == 1。 • ICC_MSRE.SRE == 1。

与GICv2向后兼容的其他行为在第14章_传统操作和不对称配置_中描述。

注意

在支持传统操作的GIC中,所有架构化的GIC寄存器都可以进行内存映射访问。

除非另有说明,本手册描述了在启用亲和性路由、System register访问和两种安全状态的系统中的GICv3架构。这意味着:

-

GICD_CTLR.ARE_NS == 1。

-

• GICD_CTLR.ARE_S == 1。 • GICD_CTLR.DS == 0。

对于在AArch64状态下的操作:

-

ICC_SRE_EL1.SRE == 1,对于该寄存器的安全和非安全副本。

-

ICC_SRE_EL2.SRE == 1。

-

ICC_SRE_EL3.SRE == 1。

对于在AArch32状态下的操作:

-

ICC_SRE.SRE == 1。

-

ICC_HSRE.SRE == 1。

-

ICC_MSRE.SRE == 1。

从GICv3开始,ARE和SRE控制位设置为0的传统操作已被弃用,如果PE实现Secure EL2则被移除。有关传统操作的更多信息,请参阅第14章_传统操作和不对称配置_。

GICv3.1特定的变更

GICv3.1增加了对Memory Partitioning and Monitoring、扩展SPI范围、扩展PPI范围以及对Secure EL2支持的支持。

GICv3.2特定的变更

GICv3.2增加了对Armv8-R AArch64的支持。

GICv4特定的变更

GICv4增加了对直接向VM注入虚拟中断的支持,无需涉及管理程序。直接注入仅由实现至少一个将中断转换为LPI的ITS的系统支持。

GICv4.1特定的变更

GICv4.1扩展了直接注入支持,也可以处理虚拟SGI。GICv4.1改变了某些GICv4数据结构的处理方式。

1.2 术语

本手册中的架构描述使用与Armv8架构相同的术语。有关此术语的更多信息,请参阅_Arm[®] Architecture Reference Manual, Armv8, for Armv8-A architecture profile_的A部分介绍。

此外,在适当的地方使用AArch64 System register名称,优先于列出AArch32和AArch64 System register名称。AArch64寄存器名称上的EL _x_后缀表示可以访问该寄存器的最低异常级别。各个AArch64 System register描述包含对提供相同功能的AArch32 System register的引用。

以下部分定义了本手册中使用的架构术语:

-

中断类型 .

-

中断状态 .

-

处理中断的模型 .

-

其他术语 .

1.2.1 中断类型

实现GIC架构的设备可以控制_外设中断_。外设中断通常通过到GIC的物理信号断言。GIC架构定义了以下类型的外设中断:

Locality-specific Peripheral Interrupt (LPI)

LPI是一个有针对性的外设中断,被路由到亲和性层次结构中的特定PE:

-

在启用两种安全状态的系统中,LPI总是Non-secure Group 1中断。

-

LPI具有边缘触发行为。

-

LPI可以使用ITS路由。

-

LPI没有活动状态,因此不需要显式去激活。

-

LPI总是基于消息的中断。

有关更多信息,请参阅_LPI_。

Private Peripheral Interrupt (PPI)

这是一个针对单个特定PE的外设中断,不同的PE可以使用相同的中断号来指示不同的事件:

-

PPI可以是Group 0中断、Secure Group 1中断或Non-secure Group 1中断。

-

PPI可以支持边缘触发或电平敏感行为。

-

PPI永远不会使用ITS路由。

-

PPI具有活动状态,因此需要显式去激活。

注意

通常,期望PPI被每个PE上相同中断源的不同实例使用,从而允许PE特定事件使用通用中断号,如来自私有定时器的中断。

Shared Peripheral Interrupt (SPI)

这是一个外设中断,Distributor可以将其路由到可以处理该中断的指定PE,或者路由到系统中已配置为接受此类中断的一组PE中的某个PE:

-

SPI可以是Group 0中断、Secure Group 1中断或Non-secure Group 1中断。

-

SPI可以支持边缘触发或电平敏感行为。

-

SPI永远不会使用ITS路由。

-

SPI具有活动状态,因此需要显式去激活。

有关更多信息,请参阅_Shared Peripheral Interrupts_。有关Distributor的更多信息,请参阅第3章_GIC分区_。

Software Generated Interrupt (SGI)

SGI通常用于处理器间通信,并通过向GIC中的SGI寄存器写入来生成:

-

SGI可以是Group 0中断、Secure Group 1中断或Non-secure Group 1中断。

-

SGI具有边缘触发行为。

-

SGI永远不会使用ITS路由。

-

SGI具有活动状态,因此需要显式去激活。

有关更多信息,请参阅_Software Generated Interrupts_。

边缘触发的中断具有以下属性:

- 在检测到中断信号的上升沿时断言,然后无论信号状态如何,保持断言直到软件确认中断。

有关边缘触发的基于消息的中断的信息,请参阅基于消息的中断。

电平敏感的中断具有以下属性:

-

当中断信号电平为活动状态时断言,当电平不为活动状态时取消断言。

-

由软件显式取消断言。

1.2.2 中断状态

以下状态适用于GIC和连接的PE之间的每个接口:

非活动 不活动或不挂起的中断。 挂起 在硬件中被识别为断言或由软件生成,并等待目标PE处理的中断。

活动 已被PE确认并正在处理的中断,因此在初始中断不再活动之前,同一中断的另一个断言不会作为中断呈现给PE。

LPI没有活动状态,在被PE确认时转换为非活动状态。

活动和挂起 从中断的一次断言活动,并从后续断言挂起的中断。

LPI没有活动和挂起状态,在被PE确认时转换为非活动状态。

GIC维护每个支持的中断的状态。状态机定义了中断状态之间可能的转换,并且对于每种中断类型,定义了导致转换的条件。有关更多信息,请参阅_中断处理状态机_。

1.2.3 处理中断的模型

在多处理器实现中,存在以下处理中断的模型:

有针对性的分发模型

此模型适用于所有PPI和所有LPI。它也适用于:

-

在非传统操作期间的SPI,如果GICD_IROUTER

.Interrupt_Routing_Mode == 0。 -

在传统操作期间,当GICD_CTLR.ARE_* == 0时,如果在适当的GICD_ITARGETSR

字段中只有一位== 1。

由软件指定的目标PE接收中断。

有针对性的列表模型

此模型仅适用于SGI。多个PE独立接收中断。当PE确认中断时,只为该PE清除中断挂起状态。中断对每个PE保持挂起,直到被PE确认。

N选1模型

此模型仅适用于SPI。中断针对指定的一组PE,并且只在该组中的一个PE上执行。选择哪个PE执行中断是以IMPLEMENTATION DEFINED的方式决定的。架构对可以选择哪些PE应用限制,请参阅_启用中断分发_。

注意

-

Arm GIC架构保证N选1中断仅呈现给目标PE集合中列出的一个PE。

-

N选1中断可能呈现给一个PE,其中该中断不是最高优先级中断,或者中断被ICC_PMR_EL1或在PE内屏蔽。请参阅_中断生命周期_。

对于传统操作期间的SPI,当在目标寄存器中指定了多个目标PE时,此模型适用。

如果有多个PE可以处理中断,硬件实现一种机制来确定哪个PE激活中断。

1.2.4 其他术语

以下其他术语在本手册中使用:

空闲优先级

在GICv3中,空闲优先级0xFF是当该接口上没有中断活动时从ICC_RPR_EL1读取的运行优先级。在传统操作期间,从GICC_RPR读取的空闲优先级是IMPLEMENTATION DEFINED的,如在GICv2中一样。

Interrupt Identifier (INTID)

唯一标识具有相关事件及其源的中断的数字空间。然后将中断路由到一个或多个PE进行处理。PPI和SGI中断号对每个PE是本地的。SPI和LPI对物理域有全局中断号。有关更多信息,请参阅_INTID_。

Interrupt Routing Infrastructure (IRI)

Distributor、Redistributor以及可选的一个或多个ITS。有关更多信息,请参阅_GIC逻辑组件_。

基于消息的中断

基于消息的中断是由于对指定地址的内存写访问而断言的中断。物理中断可以转换为基于消息的中断。基于消息的中断可以支持电平敏感或边缘触发行为,尽管LPI总是边缘触发的。

GICv3支持两种基于消息的中断机制:

- 用于传送SPI的机制,其中指定的地址保存在Distributor中。在这种情况下,基于消息的中断可以是电平敏感或边缘触发的。

• 用于传送LPI的机制,其中指定的地址保存在ITS(如果实现了ITS)或Redistributor中。

Arm建议在支持PCIe的系统中使用LPI来提供MSI和MSI-X功能的支持。有关更多信息,请参阅第5章_局部特定外设中断和ITS_。GICv3还包括对使用基于消息的中断信号SPI的架构化支持,请参阅_Shared Peripheral Interrupts_。

物理中断

针对物理PE的中断是物理中断。它通过PE连接的物理CPU interface向PE发出信号。

运行优先级

在任何给定时间,CPU interface的运行优先级要么是:

-

活动中断的组优先级,该接口上没有进行优先级下降。

-

如果接口上没有没有进行优先级下降的活动中断,运行优先级是空闲优先级0xFF。

足够优先级

GIC CPU interface将启用的挂起中断的优先级与以下所有内容进行比较,以确定中断是否具有足够的优先级:

-

优先级掩码寄存器ICC_PMR_EL1。

-

接口的抢占设置,如ICC_BPR0_EL1和ICC_BPR1_EL1所示。

-

当前运行优先级,如CPU interface的ICC_RPR_EL1所示。

-

如果中断具有足够的优先级,则向连接的PE发出信号。

虚拟中断

针对VM的中断是虚拟中断。它由关联的虚拟CPU interface发出信号。有关更多信息,请参阅第6章_虚拟中断处理和优先级_。

维护中断

一个物理中断,它向管理程序发出与VM上中断处理相关的关键事件信号,以允许管理程序跟踪这些事件。这些事件由管理程序处理,包括启用和禁用特定组的中断。有关更多信息,请参阅_维护中断_。

1.3 支持的配置和兼容性

在Armv8-A中,EL2和EL3是可选的,PE可以支持这些异常级别中的一个、两个或都不支持。但是:

-

PE需要EL3来支持安全和非安全状态。

-

PE需要EL2来支持虚拟化。

-

如果没有实现EL3,则只有一个安全状态。该安全状态要么是安全状态,要么是非安全状态。

GICv3根据_Arm[®] Architecture Reference Manual, Armv8, for Armv8-A architecture profile_中描述的_相互处理_规则,支持所有这些配置的中断处理,以及在AArch32状态和AArch64状态下的执行。

1.3.1 亲和性路由配置

GICv3架构支持亲和性路由。它提供对以下情况的可选支持:

-

不对称配置,其中为非安全状态启用亲和性路由,为安全状态禁用亲和性路由。这为安全传统环境提供了支持。

-

仅传统环境,其中为安全状态和非安全状态都禁用亲和性路由。

1.3.2 System register配置

当为两种安全状态的执行都启用亲和性路由时,必须配置GIC使用System register访问来处理物理中断。架构不支持为安全状态启用亲和性路由,而不为该安全状态配置System register访问。以这种方式配置GIC会导致UNPREDICTABLE行为。当为非安全状态的执行启用亲和性路由时,GIC架构可选地支持虚拟中断的传统操作,即在EL2执行的管理程序控制下的非安全EL1的传统中断处理。

1.3.3 GIC控制和配置

许多GIC寄存器以不同形式提供,以允许有效的中断处理:

-

用于两种安全状态。

-

用于不同的中断组。

-

对GICv3使用System register访问或对传统操作使用内存映射访问。

当启用System register访问时,GIC架构的控制和配置由架构化的System register和定义GIC程序员模型的相关访问处理。有关更多信息,请参阅第12章_程序员模型_。

一些寄存器总是内存映射的,而其他寄存器在GICv3中使用System register访问,在传统操作中使用内存映射访问。

表1-1显示了总是内存映射的寄存器。

表1-1 内存映射寄存器

| 短寄存器名中的前缀 | 寄存器 |

|---|---|

| GICD | Distributor寄存器 |

| GICR | Redistributor寄存器a |

| GITS | ITS寄存器b |

-

a. 每个PE都有一份Redistributor寄存器的副本。

-

b. 一个实现中可以有多个ITS。每个ITS都有自己的GITS寄存器副本。

表1-2显示了传统操作中内存映射的寄存器,但在启用System register访问时在GICv3中被System register访问替代。

表1-2 传统操作的内存映射寄存器

| 短寄存器名中的前缀 | 寄存器 |

|---|---|

| GICC | 物理CPU interface寄存器 |

| GICV | 虚拟CPU interface寄存器 |

| GICH | 虚拟接口控制寄存器 |

注意

-

在非安全EL1执行的操作系统使用GICC_*或GICV_*寄存器来控制中断,并且不知道差异。

-

GICR_*和GITS_*寄存器是在GICv3中引入的。

表1-3显示了当启用System register访问时GICv3支持的寄存器。

表1-3 System register

| 短寄存器名中的前缀 | 访问的System register |

|---|---|

| ICC | 物理CPU interface寄存器 |

| ICV | 虚拟CPU interface寄存器 |

| ICH | 虚拟接口控制寄存器 |

对虚拟化的Armv8支持和PE操作的异常级别决定是访问物理CPU interface寄存器还是虚拟CPU interface寄存器。

有关寄存器名称和影响使用哪个寄存器的因素的更多信息,请参阅_GIC System register访问_。

1.3.4 对Armv8架构状态的引用

表1-4显示了与GIC操作一起使用或影响GIC操作的Armv8架构状态。

表1-4 影响GIC操作的Armv8架构状态

| AArch64 状态 | AArch32 字段 状态 | 目的 字段 |

|---|---|---|

| PSTATEa | A PSTATEa I F | A SError中断掩码位(AArch64状态)异步中止掩码位(AArch32状态)I IRQ掩码位 F FIQ掩码位 |

| - | - DFSR - | STATUS/FS 故障状态 ExT 外部中止类型 |

| ESR_ELx | EC HSR IL ISS | EC 异常类别 IL 同步异常的指令长度 ISS 指令特定综合征 |

| HCR_EL2 | AMO HCR IMO FMO RW VSE VI VF TGE | AMO SError中断路由(AArch64状态)异步外部中止中断路由(AArch32状态)IMO 物理IRQ路由 FMO 物理FIQ路由 RES0 较低异常级别的执行状态控制(AArch64状态)VA 虚拟SError中止异常(AArch64状态)虚拟异步中止异常(AArch32状态)VI 虚拟IRQ中断 VF 虚拟FIQ中断 TGE 陷阱通用异常 |

| HSTR_EL2 | T | T |

| ID_AA64PFR0_EL1 | GIC - | - System register GIC接口支持 |

| ID_PFR1_EL1 | GIC ID_PFR1 | GIC System register GIC CPU interface支持 |

| ISR_EL1 | A ISR | A SError挂起(AArch64状态)外部中止挂起(AArch32状态) |

表1-4 影响GIC操作的Armv8架构状态(续)

| AArch64 状态 | AArch32 字段 状态 | 目的 字段 |

|---|---|---|

| MPIDR_EL1 | Aff3 MPIDR Aff2 Aff1 Aff0 | - 亲和性级别3 Aff2 亲和性级别2 Aff1 亲和性级别1 Aff0 亲和性级别0 |

| SCR_EL3 | RW SCR EA FIQ IRQ NS EEL2 | RES0 较低异常级别的执行状态控制(仅AArch64状态)EA SError中断路由(AArch64状态)外部中止中断路由(AArch32状态)FIQ 物理FIQ路由 IRQ 物理IRQ路由 NS 非安全位 - 安全EL2启用 |

- a. 进程状态PSTATE是进程状态信息的抽象。有关更多信息,请参阅_Arm[®] Architecture Reference Manual, Armv8, for Armv8-A architecture profile_。

有关这些寄存器和字段的更多信息,请参阅_Arm[®] Architecture Reference Manual, Armv8, for Armv8-A architecture profile_。

1.3.5 不支持传统操作的GICv3

在不支持传统操作的实现中,亲和性路由和System register访问是永久启用的。这意味着相关的控制位是RAO/WI。表1-5显示了受此影响的寄存器字段。

表1-5 亲和性路由和System register访问的控制位

| AArch64寄存器 | AArch32寄存器 | 内存映射寄存器 |

|---|---|---|

| ICC_SRE_EL1.SREa | ICC_SRE.SREa | - |

| ICC_SRE_EL2.SRE | ICC_HSRE.SRE | - |

| ICC_SRE_EL3.SRE | ICC_MSRE.SRE | - |

| - | - | GICD_CTLR.ARE_S |

| - | - | GICD_CTLR.ARE_NS |

a. 该寄存器有安全副本和非安全副本。

如果支持安全虚拟化,这是唯一允许的配置。

1.3.6 支持传统操作的GICv3

传统操作_是与GICv2的有限向后兼容形式,提供给使用GICv3的系统运行使用GICv2的代码,前提是此代码满足本节描述的限制。传统操作在GICv3中是可选的。请参阅_中断的传统支持和不对称配置。

在支持传统操作的GICv3实现中,最多八个PE,其对内存映射寄存器接口的个别支持是IMPLEMENTATION DEFINED,可作为给定VM内的物理或虚拟中断目标。这是IMPLEMENTATION DEFINED:

-

传统操作是否适用于两种安全状态的执行,还是仅适用于安全状态的执行。

-

在非安全EL1执行时,传统操作是否仅在虚拟CPU interface中可用。

在GICv3中,以下限制适用于传统操作:

- GICv2功能GICC_CTLR.AckCtl在GICv2中已被弃用,在GICv3中不受支持。相应地,即使在传统模式下,行为就像GICv2中描述的GICC_CTLR.AckCtl位是RAZ/WI一样。

注意

在支持传统操作的GICv3实现中,当GICV_CTLR.AckCtl设置为1时,允许VM控制非安全中断。但是,Arm弃用了GICV_CTLR.AckCtl的使用。

-

不支持GICv2配置锁定功能和相关的CFGSDISABLE输入信号。

-

在EL2执行的管理程序只能控制它执行的PE上的虚拟中断,不能控制其他PE上的虚拟中断。

对于传统操作,支持不对称配置,其中:

-

在非安全状态和EL3启用亲和性路由和System register访问。

-

在安全EL1禁用亲和性路由和System register访问。

这允许在安全EL1运行的安全操作系统使用传统功能,前提是它不配置非安全中断。

在GICv2中,在安全状态执行的软件可以使用GICC_AIAR、GICC_AEOIR、GICC_AHPPIR和GICC_ABPR来控制非安全状态的中断。在不对称配置中没有等价功能。

Chapter 2: 中断的分发和路由

本章描述使用亲和性路由向目标 PE 分发和路由中断,以及中断 ID 的分配。包含以下部分:

-

Distributor 和 Redistributor 。

-

INTID 。

-

亲和性路由 。

2.1 Distributor 和 Redistributor

Distributor 提供 SPI 的路由配置,并保存所有相关的路由和优先级信息。

Redistributor 提供 PPI 和 SGI 的配置设置。

Redistributor 总是在有限时间内向 CPU interface 呈现具有最高优先级的待处理中断。有关中断优先级排序的更多信息,请参见 中断优先级排序 。

最高优先级待处理中断可能因以下原因而改变:

-

先前的最高优先级中断已被确认。

-

先前的最高优先级中断已被抢占。

-

先前的最高优先级中断被移除且不再有效。

-

组中断使能已被修改。

-

PE 不再是参与 PE。请参见 参与节点 。

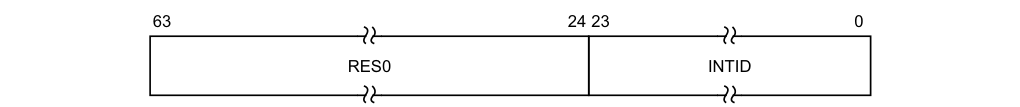

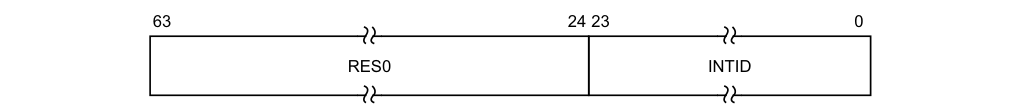

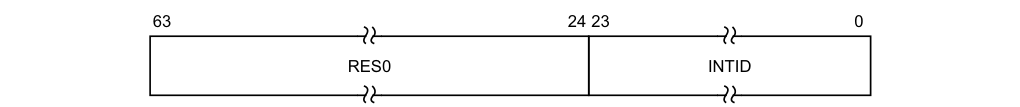

2.2 INTID

中断使用 ID 号(INTID)标识。GICv3 支持的 INTID 范围是 IMPLEMENTATION DEFINED,根据以下规则:

-

对于 Distributor 和 Redistributor 支持的 INTID 位数:

-

如果不支持 LPI,Distributor 中的 ID 空间限制为 10 位。这与 GIC 架构的早期版本相同。

-

如果支持 LPI,INTID 字段在 14-24 位范围内是 IMPLEMENTATION DEFINED,如 GICD_TYPER 的寄存器描述中所述。

注意

可以通过 GICR_PROPBASER 配置 Redistributor 使用比 GICD_TYPER 指定的更少的位数。

-

对于 ITS 支持的 INTID 位数: — 如果支持 LPI,INTID 字段在 14-24 位范围内是 IMPLEMENTATION DEFINED。

-

INTID 字段的大小由 GITS_TYPER.IDbits 定义。

必须对 ITS 进行编程,以便转发到 Redistributor 的中断在该 Redistributor 支持的中断范围内,否则行为是 UNPREDICTABLE。

-

对于 CPU interface 支持的 INTID 位数:

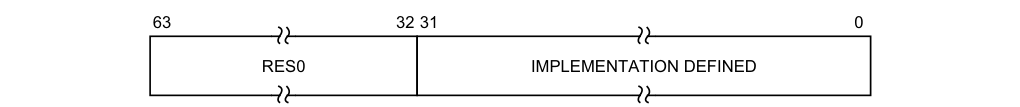

- GICv3 CPU interface 支持 16 位或 24 位 INTID 字段,选择是 IMPLEMENTATION DEFINED。支持的物理中断标识符位数由 ICC_CTLR_EL1.IDbits 和 ICC_CTLR_EL3.IDbits 指示。

有效的 INTID 空间由 CPU interface 和 Distributor 中的实现大小决定。将大于支持大小的 INTID 转发到 CPU interface 是编程错误。

未使用的 INTID 位为 RAZ。这意味着任何受影响的位字段都是零扩展的。

表 2-1 显示了 INTID 空间如何按中断类型划分。

表 2-1 INTID

| INTID | 中断类型 | 详细信息 | 注释 |

|---|---|---|---|

| 0 – 15 | SGI | 这些中断对 CPU interface 是本地的。 | INTID 0-1023 与 GIC 架构的早期版本兼容。 |

| 16 – 31 | PPI | 这些中断对 CPU interface 是本地的。 | (同上) |

| 32 – 1019 | SPI | Distributor 可以路由到特定 PE 或系统中任何参与节点 PE 的共享外设中断,请参见 参与节点。 | |

| 1020 – 1023 | 特殊中断号 | 为特殊用途保留的中断 ID,如 特殊 INTID 中所述。 | |

| 1024 – 1055 | - | 保留 | - |

| 1056 – 1119 | PPI | 扩展 PPI。这些中断对 CPU interface 是本地的。 | INTID 1056-1119 与 GIC 架构的早期版本不兼容。此范围由 GICv3.1 架构支持。 |

| 1120 – 4095 | - | 保留 | - |

| 4096 – 5119 | SPI | 扩展 SPI。 | 由 GICv3.1 架构支持。 |

| 5120 – 8191 | - | 保留 | |

| 8192 – IMPLEMENTATION DEFINED | LPI | 路由到特定 PE 的外设硬件中断。 | - |

注意 Arm 推荐的 PPI INTID 分配由服务器基础系统架构提供,请参见 Arm[®] Server Base System Architecture (SBSA) 。

GICv4 架构通过支持 vPEID 以及 INTID 空间为每个 VM 提供唯一的 INTID 空间。有关 VM 的更多信息,请参见 关于 GIC 对虚拟化的支持 ,有关 vPEID 的更多信息,请参见 中断转换服务 。

Arm 强烈建议实现的中断分组使用最低的 INTID 号和尽可能小的 INTID 范围。这减少了必须实现的内存中关联表的大小,以及发现例程必须检查的大小。

Arm 强烈建议软件保留:

-

INTID0 - INTID7 用于 Non-secure 中断。

-

INTID8 - INTID15 用于 Secure 中断。

2.2.1 特殊 INTID

GIC 架构为特殊用途保留的 INTID 列表如下:

1020 GIC 返回此值以响应在 EL3 读取 ICC_IAR0_EL1 或 ICC_HPPIR0_EL1,指示被确认的中断是预期在 Secure EL1 处理的中断。此 INTID 仅在 PE 使用 AArch64 状态在 EL3 执行时,或者 PE 在 AArch32 状态下以 Monitor 模式执行时返回。

当 ICC_CTLR_EL3.RM == 1 时,此值也可以由在 EL3 读取 ICC_IAR1_EL1 或 ICC_HPPIR1_EL1 返回,请参见 非对称操作和 ICC_CTLR_EL3.RM 的使用 。

1021 GIC 返回此值以响应在 EL3 读取 ICC_IAR0_EL1 或 ICC_HPPIR0_EL1,指示被确认的中断是预期在 Non-secure EL1 或 EL2 处理的中断。此 INTID 仅在 PE 使用 AArch64 状态在 EL3 执行时,或者 PE 在 AArch32 状态下以 Monitor 模式执行时返回。当 ICC_CTLR_EL3.RM == 1 时,此值也可以由在 EL3 读取 ICC_IAR1_EL1 或 ICC_HPPIR1_EL1 返回,请参见 非对称操作和 ICC_CTLR_EL3.RM 的使用。

1022 此值仅适用于传统操作。有关更多信息,请参见 特殊 INTID 1022 的使用。

1023 如果没有具有足够优先级的待处理中断可以向 PE 发出信号,或者如果最高优先级待处理中断不适合以下条件,则此值作为中断确认的响应返回:

- 当前安全状态。

- 与系统寄存器关联的中断组。

注意 这些 INTID 不需要中断结束或停用。

有关特殊 INTID 使用的更多信息,请参见以下寄存器的描述:

-

ICC_IAR0_EL1。

-

ICC_IAR1_EL1。

-

ICC_HPPIR0_EL1。

-

ICC_HPPIR1_EL1。

2.2.2 混合 INTID 大小的实现

实现可能选择为 GIC 的不同部分实现不同的 INTID 大小,受以下规则约束:

-

PE 可以实现 16 位或 24 位 INTID。

注意

系统可能包含支持 16 位 INTID 的 PE 和支持 24 位 INTID 的 PE 的混合。

-

Distributor 和 Redistributor 必须全部实现相同数量的 INTID 位。

-

在支持 LPI 的系统中,Distributor 和所有 Redistributor 必须实现至少 14 位 INTID。在 Distributor 和 Redistributor 中实现的位数不得超过系统中任何 PE 实现的最小位数。

注意 因为中断可能针对任何 PE,每个 PE 必须能够接收 Redistributor 可以发送的最大 INTID。这意味着 Redistributor 支持的 INTID 大小不能超过系统中每个 PE 支持的最小 INTID 大小。

-

在不支持 LPI 的系统中,Distributor 和所有 Redistributor 必须实现至少 5 位 INTID,不能实现超过 10 位 INTID。对于 GIC 版本 3.1,不能实现超过 13 位 INTID。

-

在包含一个或多个 ITS 的系统中,ITS 可以实现任何值,最多包括 Distributor 和 Redistributor 支持的位数,最少为 14 位,这是 LPI 支持所需的最小位数。

2.2.3 有效中断 ID 检查伪代码

以下伪代码描述了 GIC 如何检查物理中断的 INTID 是否有效:

// InterruptIdentifierValid()

// ==========================

boolean InterruptIdentifierValid(bits(64) data, boolean lpiAllowed)

// First check whether any out of range bits are set

integer N = CPUInterfaceIDSize();

if !IsZero(data<63:N>) then

if GenerateLocalSError() then

// Reporting of locally generated SEIs is supported

IMPLEMENTATION_DEFINED "SError INVALID_INTERRUPT_IDENTIFIER";

UNPREDICTABLE;

intID = data<INTID_SIZE-1:0>;

if !lpiAllowed && IsLPI(intID) then // LPIs are not supported

if GenerateLocalSError() then

// Reporting of locally generated SEIs is supported

IMPLEMENTATION_DEFINED "SError INVALID_INTERRUPT_IDENTIFIER";

UNPREDICTABLE;

以下伪代码描述了 GIC 如何检查虚拟中断的 INTID 是否有效:

// VirtualIdentifierValid()

// ========================

boolean VirtualIdentifierValid(bits(64) data, boolean lpiAllowed)

// First check whether any out of range bits are set

integer N = VIDBits();

if !IsZero(data<63:N>) then

if ICH_VTR_EL2.SEIS == '1' then

// Reporting of locally generated SEIs is supported

IMPLEMENTATION_DEFINED "SError INVALID_INTERRUPT_IDENTIFIER";

UNPREDICTABLE;

intID = data<INTID_SIZE-1:0>;

if !lpiAllowed && IsLPI(intID) then // LPIs are not supported

if ICH_VTR_EL2.SEIS == '1' then

// Reporting of locally generated SEIs is supported

IMPLEMENTATION_DEFINED "SError INVALID_INTERRUPT_IDENTIFIER";

UNPREDICTABLE;

// Now check for special identifiers

if IsSpecial(intID) then

return FALSE; // It is a special ID

// All the checks pass so the identifier is valid

return TRUE;

以下伪代码描述 CPU interface ID 大小函数。

// CPUInterfaceIDSize()

// Returns TRUE if the value supplied has bits above the implemented range or

// if the value supplied exceeds the maximum configured size in the

// appropriate GITS_BASERn

boolean VCPUOutOfRange(bits(16) vcpu);

2.3 亲和性路由

亲和性路由是一种基于分层地址的方案,用于识别特定的 PE 节点进行中断路由。

对于 PE,亲和性值在 AArch64 状态下在 MPIDR_EL1 中定义,在 AArch32 状态下在 MPIDR 中定义:

-

亲和性路由是一个 32 位值,由四个 8 位亲和性字段组成。这些字段是节点 a 、b 、c 和 d 。

-

使用 AArch64 状态的 GICv3 可以支持:

-

四级路由层次结构,a.b.c.d。

-

三级路由层次结构,0.b.c.d。

-

-

使用 AArch32 状态的 GICv3 仅支持三个亲和性级别。

-

ICC_CTLR_EL3.A3V、ICC_CTLR_EL1.A3V 和 GICD_TYPER.A3V 指示是否实现四级或三级亲和性。

注意 需要四级亲和性的实现必须仅支持 AArch64 状态。

在亲和性层次结构中指定节点的枚举符号为以下形式,其中 Affx 是亲和性级别 x:

Aff3.Aff2.Aff1.Aff0

在 Distributor 中使用 亲和性路由使能(ARE)位启用安全状态的亲和性路由。亲和性路由在以下情况下启用:

-

对于 Secure 中断,如果 GICD_CTLR.ARE_S 设置为 1。

-

对于 Non-secure 中断,如果 GICD_CTLR.ARE_NS 位设置为 1。

如果永久启用亲和性路由,GICD_CTLR.ARE_S 和 GICD_CTLR.ARE_NS 为 RAO/WI。

当启用亲和性路由时处理物理中断,还必须启用系统寄存器访问,请参见 GIC 系统寄存器访问 。对于其他情况,请参见第 14 章 传统操作和非对称配置 。

2.3.1 按 PE 亲和性路由 SPI 和 SGI

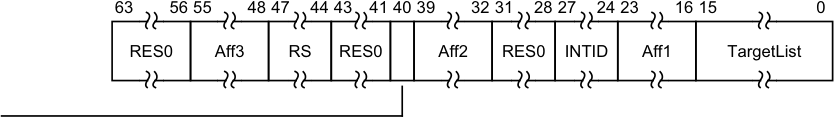

SPI 使用亲和性地址和 GICD_IROUTER

使用以下寄存器生成 SGI:

-

ICC_SGI0R_EL1。

-

ICC_SGI1R_EL1。

-

ICC_ASGI1R_EL1。

Arm 强烈建议在亲和性级别 0 仅使用 0-15 范围内的值,以与 SGI 目标列表功能对齐。请参见 软件生成中断 。

SPI 和 SGI 使用不同的寄存器进行路由:

-

SPI 使用 GICD_IROUTER

.Interrupt_Routing_Mode 进行路由: -

如果 GICD_IROUTER

.Interrupt_Routing_Mode 清除为 0,SPI 路由到由 a.b.c.d 指定的单个 PE。 -

如果 GICD_IROUTER

.Interrupt_Routing_Mode 设置为 1,SPI 路由到定义为参与节点的任何 PE: -

IRI 选择目标 PE 的机制是 IMPLEMENTATION DEFINED。

-

当 ICC_CTLR_EL3.PMHE == 1 或 ICC_CTLR_EL1.PMHE == 1 时,IRI 可能使用与 PE 关联的 ICC_PMR_EL1 寄存器来确定目标 PE。

-

-

有关参与节点的更多信息,请参见 参与节点 。

-

SGI 使用 ICC_SGI0R_EL1.IRM 和 ICC_SGI1R_EL1.IRM 进行路由:

-

如果 IRM 位设置为 1,SGI 路由到系统中所有参与的 PE,不包括发起 PE。

-

如果 IRM 位清除为 0,SGI 路由到由 a.b.c.targetlist 指定的 PE 组。

-

2.3.2 参与节点

配置为使用 1 of N 分发模型的启用 SPI 在以下情况下可以针对 PE:

-

GICR_WAKER.ProcessorSleep == 0 且中断的中断组在 PE 上启用。

-

GICD_CTLR.E1NWF == 1。

-

GICR_TYPER.DPGS == 1,且对于中断的中断组,GICR_CTLR.{DPG1S, DPG1NS, DPG0} == 0。

有关使用 1 of N 分发模型时 PE 是否可以被选择为目标的更多信息,请参见 GICR_CTLR,Redistributor 控制寄存器第 12-621 页 。

有关启用中断和中断组的更多信息,请参见 启用中断分发 。

2.3.3 更改亲和性路由使能

本手册描述了在启用亲和性路由的系统中的 GICv3 架构。这意味着:

-

GICD_CTLR.ARE_NS == 1。

-

GICD_CTLR.ARE_S == 1。

如果 GICD_CTLR.ARE_NS 或 GICD_CTLR.ARE_S 的值从 1 更改为 0,结果是 UNPREDICTABLE。

当 GICD_CTLR.DS == 0 时:

-

将 GICD_CTLR.ARE_S 从 0 更改为 1 是不可预测的,除非以下所有条件都适用:

-

GICD_CTLR.EnableGrp0 == 0。

-

GICD_CTLR.EnableGrp1S == 0。

-

GICD_CTLR.EnableGrp1NS == 0。

-

-

将 GICD_CTLR.ARE_NS 从 0 更改为 1 是不可预测的,除非 GICD_CTLR.EnableGrp1NS == 0。

当 GICD_CTLR.DS == 1 时:

-

将 GICD_CTLR.ARE 从 0 更改为 1 是不可预测的,除非以下所有条件都适用: — GICD_CTLR.EnableGrp0 == 0。

- GICD_CTLR.EnableGrp1 == 0。

注意 清除 GICD_CTLR.EnableGrp0、GICD_CTLR.EnableGrp1S 或 GICD_CTLR.EnableGrp1NS(视情况而定)的效果必须在将 GICD_CTLR.ARE_S 或 GICD_CTLR.ARE_NS 从 0 更改为 1 时可见。软件可以轮询 GICD_CTLR.RWP 来检查清除 GICD_CTLR.EnableGrp0、GICD_CTLR.EnableGrp1S 或 GICD_CTLR.EnableGrp1NS 位的写入是否已完成。

Chapter 3: GIC 分区

-

本章描述 GIC 逻辑分区。包含以下部分: • GIC 逻辑组件 。

-

中断旁路支持 。

3.1 GIC 逻辑组件

GICv3 架构由一组逻辑组件组成:

-

一个 Distributor 。

-

每个支持的 PE 的一个 Redistributor。

-

每个支持的 PE 的一个 CPU interface。

-

Interrupt Translation Service 组件(ITS),支持事件到 LPI 的可选转换。

Distributor、Redistributor 和 ITS 统称为 IRI。

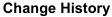

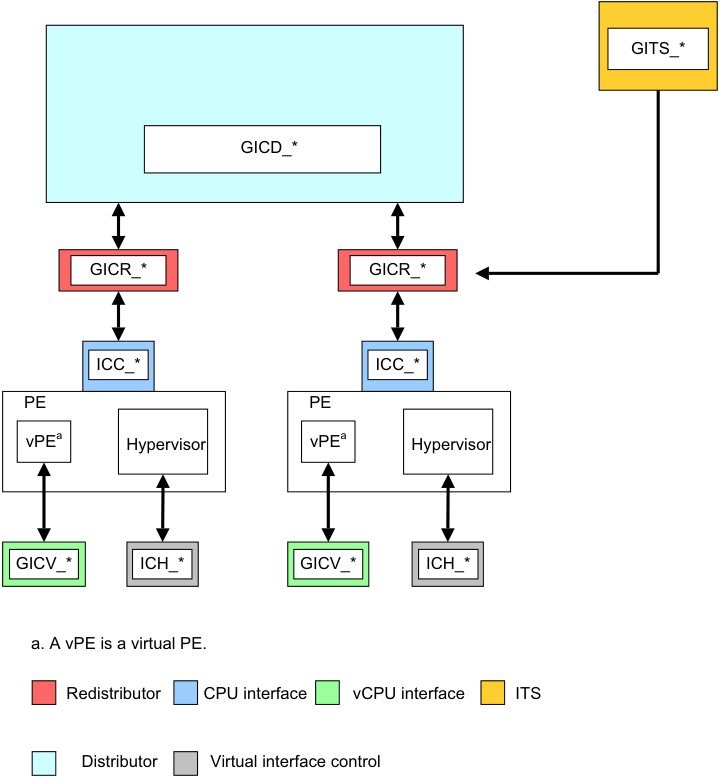

图 3-1 显示了 IRI。

图像文本

Interrupt Routing

Infrastructure (IRI)

Distributor ITS [a]

PE PE

x.y.0.0 x.y.0.1

Cluster C0

Redistributor [b] CPU interface [c]

b. 每个 PE 有一个 Redistributor。c. 每个 PE 有一个 CPU interface。

图 3-1 中断路由基础设施 CPU interface 处理所有已实现异常级别的物理中断:

-

转换为 LPI 的中断可选择通过 ITS 路由到 Redistributor 和 CPU interface。

-

PPI 直接从源路由到本地 Redistributor。

-

SPI 从源通过 Distributor 路由到目标 Redistributor 和关联的 CPU interface。

-

SGI 由软件通过 CPU interface 和 Redistributor 生成。然后通过 Distributor 路由到一个或多个目标 Redistributor 和关联的 CPU interface。

在 GICv3 中,ITS 是可选组件,将事件转换为物理 LPI。该架构还支持不需要使用 ITS 的直接 LPI。当支持 LPI 时,IMPLEMENTATION DEFINED 是否支持以下任一种:

-

通过访问 Redistributor 中的寄存器支持直接 LPI。

-

通过 ITS 提供 LPI 支持。

实现必须仅支持这些方法中的一种。

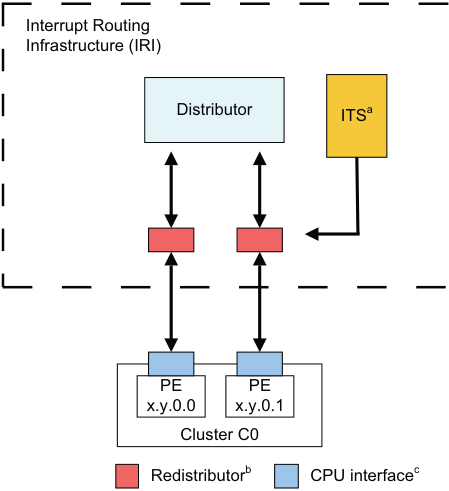

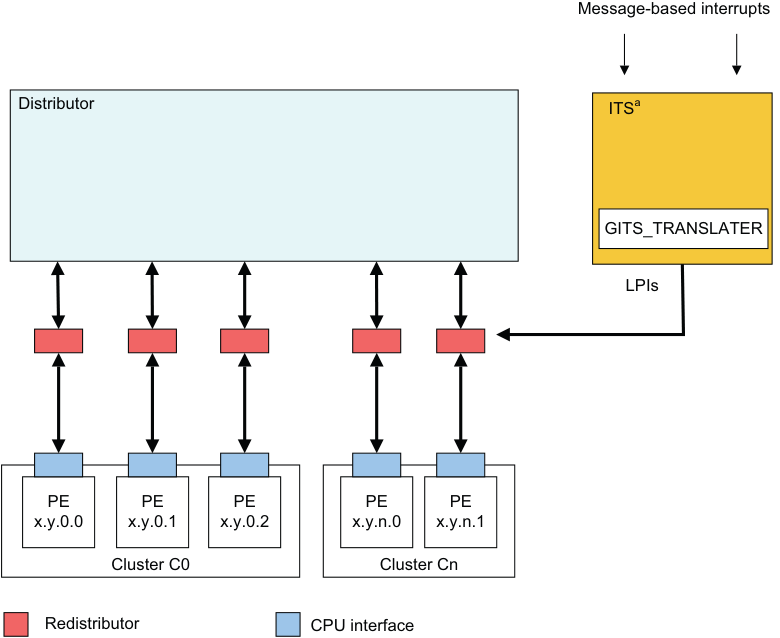

在 GICv4 中,必须包含至少一个 ITS 来提供对虚拟 LPI 直接注入的支持。 图 3-2 显示了包含 ITS 的实现中的 GIC 分区。

图像文本

SPIs

Distributor ITS [a]

LPIs

PPIs

SGIs [b] SGIs [b] SGIs [b] SGIs [b] SGIs [b]

PE PE PE PE PE

x.y.0.0 x.y.0.1 x.y.0.2 x.y.n.0 x.y.n.1

Cluster C0 Cluster Cn

Redistributor CPU interface

Distributor Interrupt Translation Service

a. ITS 的包含是可选的,一个 GIC 中可能有多个

ITS。

图 3-2 带有 ITS 的 GIC 逻辑分区

ITS 和 Redistributor 之间的通信机制是 IMPLEMENTATION DEFINED。

CPU interface 和 Redistributor 之间的通信机制也是 IMPLEMENTATION DEFINED。

注意 Arm 建议实现使用 GIC Stream 协议在 CPU interface 和 Redistributor 之间通信,请参见附录 A GIC Stream 协议接口 。

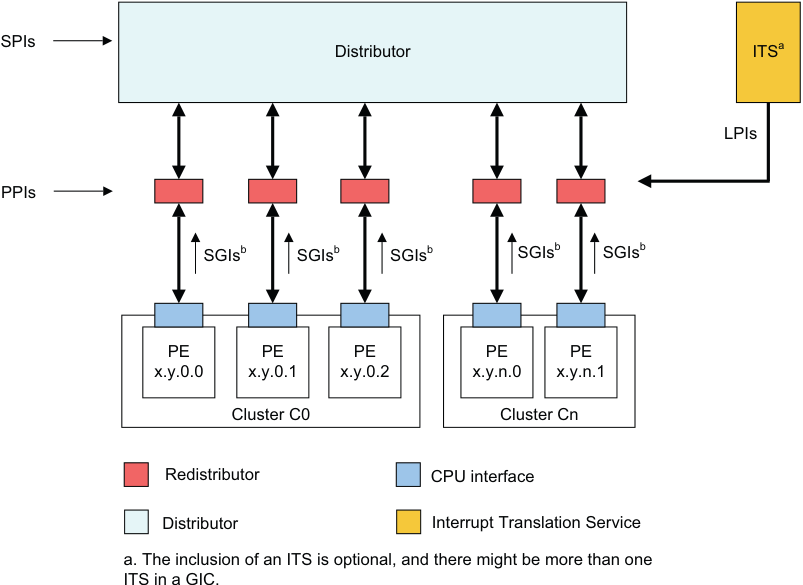

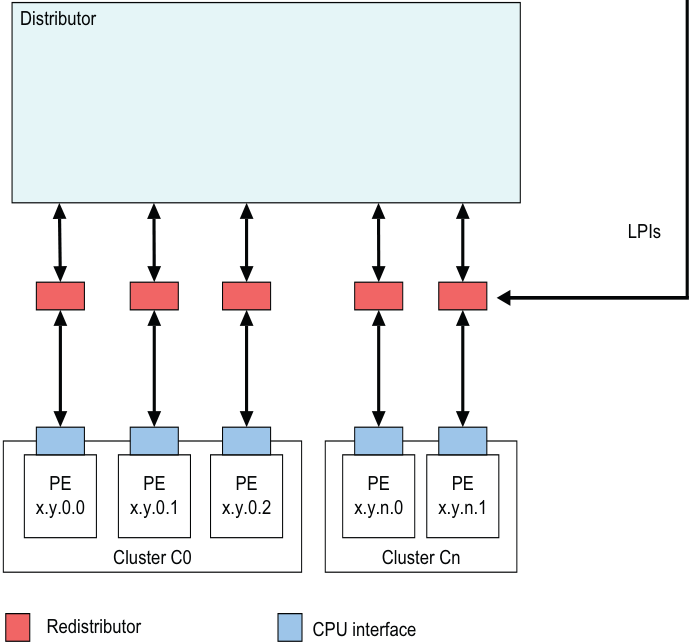

图 3-3 显示了不包含 ITS 且支持直接 LPI 的实现中的 GIC 分区。 3.1 GIC 逻辑组件

图像文本

SPIs

Distributor

LPIs

PPIs

SGIs [a] SGIs [a] SGIs [a] SGIs [a] SGIs [a]

PE PE PE PE PE

x.y.0.0 x.y.0.1 x.y.0.2 x.y.n.0 x.y.n.1

Cluster C0 Cluster Cn

Redistributor CPU interface

Distributor

a. SGI 由 PE 生成并通过 Distributor 路由。

以下列表更详细地描述了图 3-2 中描绘的组件:

Distributor

Distributor 对 SPI 和 SGI 进行中断优先级排序和分发到连接到系统中 PE 的 Redistributor 和 CPU interface。GICD_CTLR 提供以下全局设置:

-

启用亲和性路由。

-

禁用安全性。

-

启用 Secure 和 Non-secure Group 1 中断。

-

启用 Group 0 中断。

对于 SPI,Distributor 提供编程接口用于:

-

启用或禁用 SPI。

-

设置每个 SPI 的优先级。

-

每个 SPI 的路由信息。

-

将每个 SPI 设置为电平敏感或边沿触发。

-

生成基于消息的 SPI。

-

将每个 SPI 分配给中断组。

-

控制 SPI 的待处理和活动状态。

Distributor 寄存器以 GICD_ 前缀标识。

有关更多信息,请参见第 2 章 中断分发和路由 。

注意 在传统操作期间处理物理中断时,Distributor 控制 PPI 和 SGI 的配置信息。请参见第 14 章 传统操作和非对称配置 。

中断转换服务,ITS

ITS 是 GICv3 架构中的可选硬件机制,将 LPI 路由到适当的 Redistributor。软件使用命令队列配置 ITS。与 ITS 关联的内存中的表结构将与设备关联的 EventID 转换为 PE 的待处理 INTID。

ITS 在 GICv4 中不是可选的,所有 GICv4 实现必须包含至少一个 ITS。

有关更多信息,请参见 中断转换服务 。

Redistributor Redistributor 是连接到 PE 的 CPU interface 的 IRI 部分。Redistributor 使用内存中保存的数据结构保存所有物理 LPI 的控制、优先级和待处理信息。Redistributor 中的两个寄存器指向这些数据结构:

-

GICR_PROPBASER。

-

GICR_PENDBASER。

在 GICv4 中,Redistributor 还包含寄存器来处理由 ITS 转发到 Redistributor 并直接转发到 VM 的虚拟 LPI,而无需涉及 hypervisor。这被称为虚拟中断的 直接注入 到 VM。

在 GICv4 中,Redistributor 共同托管所有虚拟 LPI 的控制、优先级和待处理信息,使用内存中保存的数据结构。Redistributor 中的两个寄存器指向这些数据结构:

-

GICR_VPROPBASER。

-

GICR_VPENDBASER。

在支持 LPI 但不包含 ITS 的实现中,GICR_* 寄存器包含简单的内存映射接口来信号和控制物理 LPI。

Redistributor 提供编程接口用于:

-

识别、控制和配置支持的功能以启用中断和实现的中断路由。

-

启用或禁用 SGI 和 PPI。

-

设置 SGI 和 PPI 的优先级。

-

将每个 PPI 设置为电平敏感或边沿触发。

-

将每个 SGI 和 PPI 分配给中断组。

-

控制 SGI 和 PPI 的待处理状态。

-

控制 SGI 和 PPI 的活动状态。

-

连接的 PE 的电源管理支持。

-

当支持 LPI 时,支持关联中断属性及其待处理状态的内存中数据结构的基地址控制。

-

当支持 GICv4 时,支持关联虚拟中断属性及其待处理状态的内存中数据结构的基地址控制。

Redistributor 寄存器以 GICR_ 前缀标识。

有关 Redistributor 的更多信息,请参见 亲和性路由 和 Distributor 和 Redistributor 。

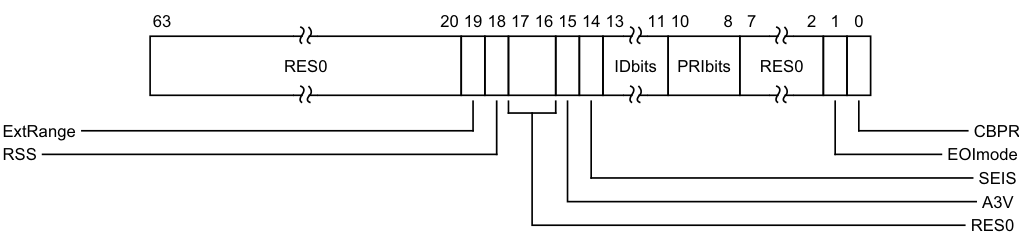

CPU interface

GIC 架构支持向系统中的 PE 提供寄存器接口的 CPU interface。每个 CPU interface 提供编程接口用于:

-

通用控制和配置,根据实现的安全状态和传统支持要求启用中断处理。

-

确认中断。

-

执行优先级下降。

-

中断的停用。

-

为 PE 设置中断优先级掩码。

-

为 PE 定义抢占策略。

-

确定 PE 的最高优先级待处理中断。

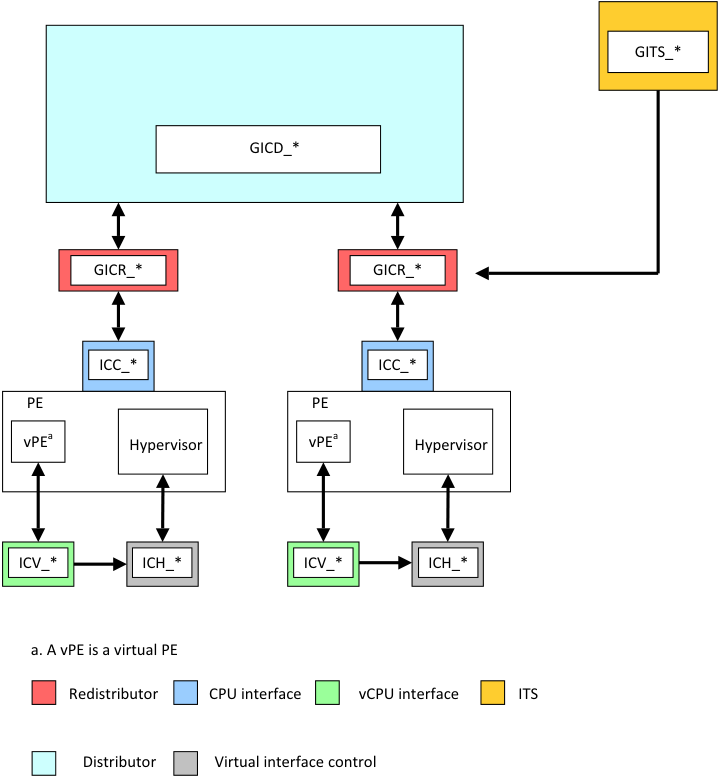

CPU interface 有几个组件:

-

允许监管级别软件控制物理中断处理的组件。与此关联的寄存器以 ICC_ 前缀标识。

-

允许监管级别软件控制虚拟中断处理的组件。与此关联的寄存器以 ICV_ 前缀标识。

-

允许 hypervisor 控制待处理中断集的组件。与此关联的寄存器以 ICH_ 前缀标识。

注意 CPU interface 中的系统寄存器与处理物理域中中断的软件相关联,或与作为 VM 一部分在 Non-secure EL1 执行相关联。HCR_EL2 的配置确定访问是针对物理资源还是虚拟资源。

在 EL2 访问的用于控制 PE 的活动、待处理以及活动和待处理虚拟中断列表的系统寄存器以 ICH_ 前缀标识。

有关处理物理中断的更多信息,请参见第 4 章 物理中断处理和优先级 。

有关处理虚拟中断的更多信息,请参见第 6 章 虚拟中断处理和优先级 。

3.2 中断旁路支持

CPU interface 可选择包含中断信号旁路,以便当接口的中断信号被禁用时,传统中断信号传递到 PE 上的中断请求输入,绕过 GIC 功能。

是否支持旁路是 IMPLEMENTATION DEFINED。

确定是否使用 GICv3 FIQ 和 IRQ 输出或旁路信号的控制因是否启用系统寄存器访问而异。

当启用系统寄存器访问时,在最高实现异常级别使用 ICC_SRE_EL1、ICC_SRE_EL2 或 ICC_SRE_EL3 中的两个位来控制旁路禁用,视情况而定:

-

对于 FIQ 旁路,这是 DFB 位。

-

对于 IRQ 旁路,这是 DIB 位。

当启用系统寄存器访问时使用此旁路机制。有关传统操作期间旁路支持的信息,请参见 传统操作和旁路支持 。

GIC 支持的中断组分配给 FIQ 和 IRQ,如 中断分组 中所述。当启用旁路时,必须在 CPU interface 禁用中断组,否则 GICv3 实现的行为是 UNPREDICTABLE。这意味着:

-

当 ICC_SRE_ELx.DFB == 0 时,ICC_IGRPEN0_EL1.Enable 必须为 0。

-

当 ICC_SRE_ELx.DIB == 0 时,ICC_IGRPEN1_EL1.Enable 必须为 0。

有关启用中断的更多信息,请参见 启用中断分发 。

有关未启用系统寄存器访问时行为的信息,请参见第 14 章 传统操作和非对称配置 。

对于 FIQ,以下伪代码确定向 PE 发送中断信号的源。

if ICC_SRE_EL3.SRE == 1 then

if ICC_SRE_EL3.DFB == 0 then

if ICC_SRE_EL1.SRE Secure == 1 then

BypassFIQsource

else

use legacy bypass support

else

use GICv3 FIQ output

else

use legacy bypass support

对于 IRQ,以下伪代码确定向 PE 发送中断信号的源。

if ICC_SRE_EL3.SRE == 1 then

if ICC_SRE_EL3.DIB == 0 then

if ICC_SRE_EL1.SRE Secure == 1 then

BypassIRQsource

else

use legacy bypass support

else

use GICv3 IRQ output

else

use legacy bypass support

第4章:物理中断处理和优先级

本章描述了GIC中断处理和优先级的基本方面。它包含以下部分:

-

中断生命周期。

-

局部特定外设中断。

-

私有外设中断。

-

软件生成中断。

-

共享外设中断。

-

中断分组。

-

启用中断分发。

-

中断优先级。

4.1 中断生命周期

GIC中断处理基于GIC中断生命周期,这是一系列适用于使用GIC架构的任何中断的高级流程。中断生命周期为描述中断处理过程的详细步骤提供了基础。GIC还维护一个状态机,在生命周期期间控制中断状态转换。

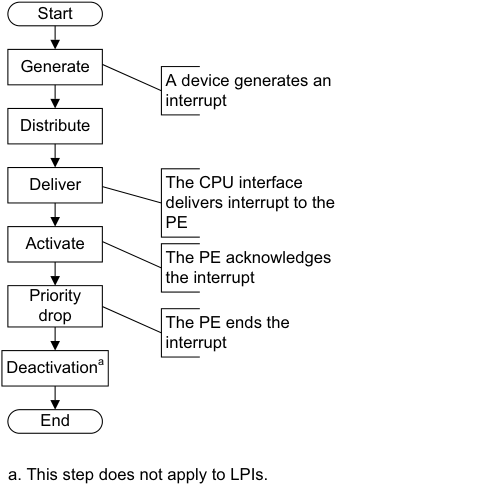

图4-1显示了物理中断的GIC中断生命周期。

图片文本

Start

Generate

A device generates an

interrupt

Distribute

Deliver The CPU interface

delivers interrupt to the

PE

Activate

The PE acknowledges

the interrupt

Priority

drop The PE ends the

interrupt

Deactivation [a]

End

a. This step does not apply to LPIs.

图4-1中的中断生命周期如下:

-

生成中断。中断由外设或软件生成。

-

分发。IRI执行中断分组、中断优先级处理,并控制中断向CPU interface的转发。

-

投递。物理CPU interface将中断投递到对应的PE。

-

激活。当在PE上运行的软件确认一个中断时,GIC将最高活跃优先级设置为被激活中断的优先级,对于SPI、SGI和PPI,中断变为活跃状态。

-

优先级下降。在PE上运行的软件向GIC发出信号,表示最高优先级中断已处理到可以下降运行优先级的程度。运行优先级然后具有中断确认之前的值。这是中断处理程序指示中断结束的点。中断结束也可以配置为同时执行中断去激活。

-

去激活。去激活清除中断的活跃状态,从而允许中断在挂起时再次被获取。LPI不需要去激活。去激活可以配置为与优先级下降同时发生,或者可以配置为稍后作为显式中断去激活操作的结果发生。后一种方法允许软件架构在将中断处理分为初始处理和调度处理方面有优势。

4.1.1 物理CPU interface

CPU interface为连接到GIC的PE提供接口。每个CPU interface连接到单个PE。

CPU interface接收由IRI优先级处理的挂起中断,并确定中断是否是在CPU interface中启用的组的成员,以及是否具有足够的优先级以向PE发送信号。在任何时候,连接的PE都可以确定:

-

其最高优先级挂起中断的INTID,通过读取ICC_HPPIR0_EL1或ICC_HPPIR1_EL1。

-

CPU interface的运行优先级,通过读取ICC_RPR_EL1。

注意

尚未进行优先级下降的最高优先级活跃中断的优先级也称为运行优先级。

当确认LPI时,中断的挂起状态在Redistributor中变为非挂起。Redistributor不为LPI维护活跃状态。

当PE在CPU interface确认SGI、PPI或SPI时,如果满足以下条件,IRI将中断状态更改为活跃:

-

它是边缘触发中断,并且自中断确认以来没有检测到另一个边缘。

-

它是电平敏感中断,并且自中断确认以来电平已去断言。

当PE在CPU interface确认SGI、PPI或SPI时,如果满足以下条件,IRI将中断状态更改为活跃和挂起:

-

它是边缘触发中断,并且自中断确认以来检测到另一个边缘。

-

它是电平敏感中断,并且自中断确认以来电平未去断言。

当PE在CPU interface确认SGI、PPI或SPI时,CPU interface可以向PE发送另一个中断信号,以抢占在PE上活跃的中断。如果没有具有足够优先级向PE发送信号的挂起中断,interface去断言向PE的中断请求信号。

中断生命周期的以下阶段在本节的其余部分中描述:

-

激活。

-

优先级下降。

-

去激活。

优先级下降和去激活可以作为单个操作执行,也可以分开,由ICC_CTLR_EL1.EOImode和ICC_CTLR_EL3.EOImode_EL3定义。

激活

中断处理程序读取相应CPU interface中Group 0中断的ICC_IAR0_EL1和Group 1中断的ICC_IAR1_EL1来确认中断。这个读取返回以下之一:

-

最高优先级挂起中断的INTID,如果该中断具有足够的优先级向PE发送信号。这是对中断确认的正常响应。

-

在特定条件下,指示特殊中断号的INTID,参见_INTID_。

读取ICC_IAR0_EL1和ICC_IAR1_EL1是否返回有效INTID取决于:

-

访问的是这两个寄存器中的哪一个。

-

PE的Security状态。

-

是否有具有足够优先级向PE发送信号的挂起中断,如果有,是否:

-

最高优先级挂起中断是Secure Group 1或Non-secure Group 1中断。

-

该中断组的中断信号发送已启用。

-

-

PE执行的Exception level。

所有中断在确认时都会修改_Active Priorities Registers_。参见_系统寄存器访问Active Priorities寄存器_。

在某些情况下,SCR_EL3.NS的值影响PE确认中断时返回的值。也就是说,当PE在EL3执行时,ICC_IAR0_EL1的Secure读取返回一个特殊中断号,指示最高优先级挂起中断所需的Security状态转换。否则,返回INTID。

对于多处理器实现中的SGI,GIC使用目标列表模型,其中一个PE确认中断对其他CPU interface上的中断状态没有影响。当PE确认中断时,中断的挂起状态仅对该PE清除。中断对其他PE保持挂起。

读取ICC_IAR0_EL1和ICC_IAR1_EL1对返回INTID状态的影响在DSB执行之后才保证可见。

优先级下降

中断确认后,对Group 0中断的ICC_EOIR0_EL1的有效写入,或对Group 1中断的ICC_EOIR1_EL1的有效写入,导致优先级下降。

对ICC_EOIR0_EL1或ICC_EOIR1_EL1的有效写入以执行优先级下降对于每个确认的中断都是必需的,即使对于没有活跃状态的LPI也是如此。优先级下降必须由激活中断的同一个PE执行。

注意 有效写入是满足以下条件的写入:

-

不是UNPREDICTABLE。

-

不被忽略。

-

不是写入不支持的或在1020-1023范围内的INTID。

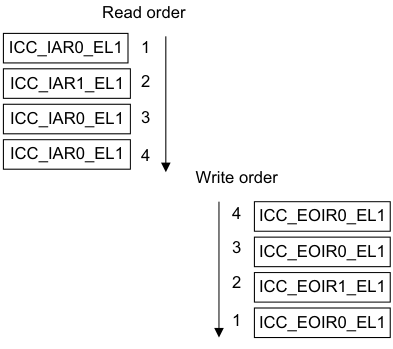

对于每个CPU interface,GIC架构要求对ICC_EOIR0_EL1和ICC_EOIR1_EL1的有效写入的顺序与从ICC_IAR0_EL1和ICC_IAR1_EL1的读取顺序完全相反,如图4-2所示。

图片文本

Read order

ICC_IAR0_EL1 1

ICC_IAR1_EL1 2

ICC_IAR0_EL1 3

ICC_IAR0_EL1 4

Write order

4 ICC_EOIR0_EL1

3 ICC_EOIR0_EL1

2 ICC_EOIR1_EL1

1 ICC_EOIR0_EL1

在优先级下降时,运行优先级从由写入ICC_EOIR0_EL1或ICC_EOIR1_EL1指示的中断的优先级降低到:

-

尚未写入ICC_EOIR0_EL1或ICC_EOIR1_EL1的最高优先级活跃中断的优先级。

-

如果没有活跃中断,则为空闲优先级0xFF。

注意 为了与GIC架构规范的可能扩展兼容,软件在确认中断时必须保留从ICC_IAR0_EL1和ICC_IAR1_EL1读取的整个寄存器值,并使用该整个值由同一PE对ICC_EOIR0_EL1和ICC_EOIR1_EL1进行相应写入。

当GICD_CTLR.DS == 0时:

-

对ICC_EOIR0_EL1的写入为Group 0中断执行优先级下降。

-

如果PE在Non-secure状态或EL3操作,对ICC_EOIR1_EL1的写入为Non-secure Group 1中断执行优先级下降。

-

在Secure状态操作时,对ICC_EOIR1_EL1的写入为Secure Group 1中断执行优先级下降。

当GICD_CTLR.DS == 1时:

-

对ICC_EOIR0_EL1的写入为Group 0中断执行优先级下降。

-

对ICC_EOIR1_EL1的写入为Group 1中断执行优先级下降。

去激活

PPI、SGI和SPI在IRI中有活跃状态,必须被去激活。

SGI和PPI必须由激活中断的PE去激活。SPI可以由不同的PE去激活。

中断去激活需要将中断状态更改为:

-

从活跃和挂起变为挂起。

-

从活跃变为非活跃。

根据Exception level和Security状态,适当CPU Interface Control Register中的ICC_CTLR_EL1.EOImode和ICC_CTLR_EL3.EOImode_EL3确定优先级下降和中断去激活是一起发生还是分别发生:

-

当CPU interface中的ICC_CTLR_EL1.EOImode或ICC_CTLR_EL3.EOImode_EL3为0时,优先级下降和中断去激活一起发生,PE写入ICC_EOIR0_EL1或ICC_EOIR1_EL1。在这种情况下,不需要写入ICC_DIR_EL1。

-

当CPU interface中的ICC_CTLR_EL1.EOImode或ICC_CTLR_EL3.EOImode_EL3为1时,优先级下降和中断去激活分离,PE写入ICC_EOIR0_EL1或ICC_EOIR1_EL1。在这种情况下:

-

当PE写入ICC_EOIR0_EL1或ICC_EOIR1_EL1时发生优先级下降。

-

中断去激活稍后发生,当PE写入ICC_DIR_EL1时。对ICC_DIR_EL1的有效写入导致Group 0或Group 1中断的中断去激活。

-

对ICC_DIR_EL1的写入没有排序要求。如果软件在以下条件为真时写入ICC_DIR_EL1,结果是不可预测的:

-

适当的EOIMode位清除为0。

-

ICC_CTLR_EL1.EOImode或ICC_CTLR_EL3.EOIMode_EL3设置为1,并且没有对ICC_EOIR0_EL1或ICC_EOIR1_EL1进行相应写入。

当ICC_CTLR_EL1.EOImode或ICC_CTLR_EL3.EOIMode_EL3 == 1但中断在Distributor中不活跃时,对ICC_DIR_EL1的写入必须被忽略。如果支持,实现可能生成系统错误。

表4-1显示了写入ICC_EOIR0_EL1或ICC_EOIR1_EL1如何影响去激活。

表4-1 写入ICC_EOIR0_EL1或ICC_EOIR1_EL1的影响

| 访问 | ICC_CTLR_EL1.EOImode或 ICC_CTLR_EL3.EOImode_EL3 | 识别的 中断 | 影响 |

|---|---|---|---|

| ICC_EOIR1_EL1 | 0 | Group 0 | 访问被忽略 |

| ICC_EOIR0_EL1 | 0 | Group 0 | 中断去激活 |

| ICC_EOIR1_EL1 | 0 | Group 1 | 中断去激活 |

| ICC_EOIR0_EL1 | 0 | Group 1 | 访问被忽略 |

| - | 1 | - | 中断保持活跃 |

当GICD_CTLR.DS == 0时,对某些寄存器的访问受到限制。参见_中断分组和安全性_。

以下伪代码确定是否为当前Exception level和Security状态设置EOImode:

// EOImodeSet()

// ============

boolean EOImodeSet()

if HaveEL(EL3) then

// EL3 is implemented so return the value appropriate to the EL and security state

if IsEL3OrMon() && ICC_SRE_EL3.SRE == '1'1 then

// In EL3

EOImode = ICC_CTLR_EL3.EOImode_EL3;

elsif IsSecure() then

EOImode = ICC_CTLR_EL3.EOImode_EL1S;

else // Non-secure

EOImode = ICC_CTLR_EL3.EOImode_EL1NS;

else

// No EL3 so return the value from ICC_CTLR_EL1

EOImode = ICC_CTLR_EL1.EOImode;

return EOImode == '1';

Security状态对ICC_DIR_EL1写入的影响

对ICC_DIR_EL1的写入的影响取决于GIC是否支持一个或两个Security状态:

-

如果GICD_CTLR.DS == 0,有效的:

- 对ICC_DIR_EL1的Secure写入去激活指定的中断,无论该中断是Group 0还是Group 1中断。- 对ICC_DIR_EL1的Non-secure写入仅在该中断是Non-secure Group 1中断时才去激活指定的中断。

-

如果GICD_CTLR.DS == 1,对ICC_DIR_EL1的有效写入去激活指定的中断,无论该中断是Group 0还是Group 1中断。

表4-2显示了对ICC_DIR_EL1的有效写入的行为。在仅支持单个Security状态的实现中,有效写入具有对ICC_DIR_EL1的Secure写入所示的行为。

表4-2 对ICC_DIR_EL1写入的行为

| 对ICC_DIR_EL1写入的Security状态和Exception level | 中断组 | GICD_CTLR.DS | SCR_EL3.IRQ | SCR_EL3.FIQ | 影响 |

|---|---|---|---|---|---|

| EL3 | x | x | x | x | 中断被去激活 |

| Secure EL1或Secure EL2 | Group 0 | x | x | 0 | 中断被去激活 |

| Secure EL1或Secure EL2 | Group 0 | x | x | 1 | 写入被忽略 |

| Secure EL1或Secure EL2 | Group 1 | x | 0 | x | 中断被去激活 |

| Secure EL1或Secure EL2 | Group 1 | x | 1 | x | 写入被忽略 |

| EL2或Non-secure EL1 | Group 0或Secure Group 1 | 0 | x | x | 写入被忽略 |

| EL2或Non-secure EL1 | Group 0 | 1 | x | 0 | 中断被去激活 |

| EL2或Non-secure EL1 | Group 0 | 1 | x | 1 | 写入被忽略 |

| EL2或Non-secure EL1 | Non-secure Group 1 | 0 | 0 | x | 中断被去激活 |

| EL2或Non-secure EL1 | Non-secure Group 1 | 0 | 1 | x | 写入被忽略 |

| EL2或Non-secure EL1 | Group 1 | 1 | 0 | x | 中断被去激活 |

| EL2或Non-secure EL1 | Group 1 | 1 | 1 | x | 写入被忽略 |

只有当SCR_EL3.EEL2 == 1时,才能进入Secure EL2。

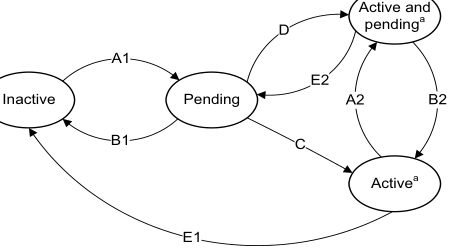

4.1.2 中断处理状态机

GIC为每个支持的中断维护状态机。中断的可能状态是:

-

非活跃。

-

挂起。

-

活跃。

-

活跃和挂起。

PPI、SGI和SPI可以具有活跃和挂起状态。活跃和挂起的中断永远不会向连接的PE发送信号。

LPI具有保存在与Redistributor相关联的内存中的挂起状态,因此也与PE相关联。这也适用于直接注入的虚拟LPI,参见_关于GICv4.0虚拟局部特定外设中断支持_。

注意 LPI没有活跃或活跃和挂起状态。

图4-3显示了中断处理状态机的实例和可能的状态转换。

图片文本

Active and

D pending [a]

A1

E2

Inactive Pending A2 B2

B1 C

Active [a]

E1

a. 当GICD_CTLR.nASSGIreq==1时不适用于SGI,

对LPI也不适用。

图4-3 中断处理状态机

注意 LPI在Redistributor中没有活跃状态,但在CPU interface中需要活跃优先级。参见第5章_局部特定外设中断和ITS_获取更多信息。

Arm期望硬件实现报告GICD_TYPER2.nASSGIcap==0,表示GICD_CTLR.nASSGIreq为RES0。

当Distributor的中断转发和CPU interface的中断信号发送启用时,引起每个状态转换的条件如下:

转换A1或A2,添加挂起状态

当中断变为挂起时发生此转换,要么是由于外设生成中断,要么是由于软件生成中断。

转换B1或B2,移除挂起状态

当中断被外设去断言时(如果中断是电平敏感中断),或当软件更改挂起状态时,发生此转换。

对于LPI,它也在中断确认时发生。

转换C,挂起到活跃

对于边缘触发的SPI、SGI和PPI,此转换在PE确认中断时发生。

对于SPI、SGI和PPI,此转换在软件从ICC_IAR0_EL1或ICC_IAR1_EL1读取INTID值时发生。

转换D,挂起到活跃和挂起

对于电平敏感的SPI、SGI和PPI,此转换在PE确认中断时发生。

转换E1或E2,移除活跃状态

对于SPI、SGI和PPI,此转换在软件去激活中断时发生。

4.2 局部特定外设中断

LPI是目标外设中断,路由到亲和性层次结构内的特定PE。在启用两个Security状态的系统中,LPI始终是Non-secure Group 1中断。LPI仅支持边缘触发行为。有关LPI的更多信息,参见_LPI_。

4.3 私有外设中断

PPI是针对单个特定PE的中断,不同的PE可以使用相同的INTID来指示不同的事件。PPI可以是Group 0中断、Secure Group 1中断或Non-secure Group 1中断。它们可以支持边缘触发或电平敏感行为。

可选的扩展PPI范围使用INTID 1056 - 1119。当GIC在legacy mode操作时,此PPI范围不可用。GICR_TYPER.PPInum指示是否支持扩展PPI范围。

注意 通常,Arm期望PPI由每个PE上相同中断源的不同实例使用,从而允许为PE特定事件(例如来自私有定时器的中断)使用通用INTID。

4.4 软件生成中断

SGI通常用于处理器间通信,通过写入GIC中的SGI寄存器生成。SGI可以是Group 0或Group 1中断,它们只能支持边缘触发行为。

与SGI生成相关的寄存器是CPU interface的一部分:

-

PE通过写入ICC_SGI1R_EL1或ICC_ASGI1R_EL1生成Group 1 SGI。

-

PE通过写入ICC_SGI0R_EL1生成Group 0 SGI。

-

路由信息作为生成SGI的寄存器写入中的位域值提供。SGI可以路由到:

-

由a.b.c.targetlist指定的PE组。这可以包括发起PE。

-

系统中的所有参与PE,除了发起PE。

-

有关更多信息,参见_按PE亲和性路由SPI和SGI_。

ICC_SGI1R_EL1允许在Secure状态执行的软件生成Secure Group 1 SGI。

ICC_SGI1R_EL1允许在Non-secure状态执行的软件生成Non-secure Group 1 SGI。

ICC_ASGI1R_EL1允许在Secure状态执行的软件生成Non-secure Group 1 SGI。

ICC_ASGI1R_EL1允许在Non-secure状态执行的软件生成Secure Group 1 SGI,如果目标PE对应的Redistributor中的GICR_NSACR设置允许的话。

ICC_SGI0R_EL1允许在Secure状态执行的软件生成Group 0 SGI。

ICC_SGI0R_EL1允许在Non-secure状态执行的软件生成Group 0 SGI,如果目标PE对应的Redistributor中的GICR_NSACR设置允许的话。

有关使用控制寄存器将SGI转发到目标PE的更多信息,参见表12-14。

4.5 共享外设中断

SPI是外设中断,Distributor可以将其路由到可以处理中断的指定PE,或路由到系统中已配置为接受此类中断的一组PE中的一个PE。SPI可以是Group 0或Group 1中断,它们可以支持边缘触发或电平敏感行为。

可选的扩展SPI范围使用INTID 4096 - 5119。当GIC在legacy mode操作时,此SPI范围不可用。GICD_TYPER.ESPI指示是否支持扩展SPI范围。

SPI可以是基于线的或基于消息的中断。

对基于消息的SPI的支持是可选的,可以通过GICD_TYPER.MBIS发现。基于消息的SPI可以是:

-

通过写入GICD_SETSPI_NSR或GICD_SETSPI_SR生成

-

通过写入GICD_CLRSPI_NSR或GICD_CLRSPI_SR清除。

写入这些寄存器的影响取决于目标SPI是否配置为边缘触发或电平敏感中断:

-

对于边缘触发中断,写入GICD_SETSPI_NSR或GICD_SETSPI_SR设置中断挂起。当中断被激活时,或通过写入GICD_CLRSPI_NSR、GICD_CLRSPI_SR或GICD_ICPENDR

清除时,中断不再挂起。 -

对于电平敏感中断,写入GICD_SETSPI_NSR或GICD_SETSPI_SR设置中断挂起。它保持挂起直到通过写入GICD_CLRSPI_NSR或GICD_CLRSPI_SR去断言。如果中断在通过写入GICD_SETSPI_NSR或GICD_SETSPI_SR断言和通过写入GICD_CLRSPI_NSR或GICD_CLRSPI_SR去激活之间被激活,则中断变为活跃和挂起。

-

对于电平敏感中断,写入GICD_ICPENDR

对通过写入GICD_SETSPI_NSR或GICD_SETSPI_SR设置为挂起的中断是否有任何影响,或者写入GICD_CLRSPI_NSR或GICD_CLRSPI_SR对通过写入GICD_ISPENDR 设置为挂起的中断是否有任何影响,是IMPLEMENTATION DEFINED。 -

确认通过写入GICD_ISPENDR

设置为挂起的中断是否清除挂起状态是IMPLEMENTATION DEFINED。

-

-

当有挂起中断时将中断配置从电平敏感更改为边缘触发,或从边缘触发更改为电平敏感,会使中断处于UNKNOWN状态。

图4-4显示基于消息的中断请求如何触发SPI。

| Wire-based | Wire-based | Wire-based | Wire-based | Wire-based | Wire-based | SPIs | SPIs | SPIs | ||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Message- | Distributor | |||||||||||||||||||||||||||||||

| based SPIs | GICD_SETSPI_SR registers | GICD_SETSPI_NSR | registers | |||||||||||||||||||||||||||||

| GICD_CLRSPI_SR registers | GICD_CLRSPI_NSR | registers | ||||||||||||||||||||||||||||||

| x.y.0.0 | PE Redistributor | Cluster C0 | x.y.0.1 | PE | x.y.0.2 | PE | CPU interface | x.y.n.0 | PE | Cluster | PE x.y.n.1 Cn |

图4-4 触发SPI

4.6 中断分组

GICv3使用_中断分组_作为将中断处理与Armv8 Exception模型和Security模型对齐的机制。

在具有两个Security状态的系统中,中断配置为以下之一:

-

Group 0物理中断:

- Arm期望这些中断在EL3处理。

-

Secure Group 1物理中断:

- Arm期望这些中断在使用Secure虚拟化的系统中在Secure EL1或Secure EL2处理。

-

Non-secure Group 1物理中断:

- Arm期望这些中断在使用虚拟化的系统中在Non-secure EL2处理,或在不使用虚拟化的系统中在Non-secure EL1处理。

在具有一个Security状态的系统中,中断配置为:

-

Group 0。

-

Group 1。

在系统级别,GICD_CTLR.DS指示GIC是否配置为一个或两个Security状态。有关Security的更多信息,参见_中断分组和安全性_。

这些中断组映射到Armv8 FIQ和IRQ异常,参见_中断分配到IRQ和FIQ信号_。

GICD_IGROUPR

GICR_IGROUPR0和GICR_IGRPMODR0配置SGI和PPI的中断组,GICR_IGROUPR

注意

当GICD_CTLR.DS == 0时,LPI始终是Non-secure Group 1中断。当GICD_CTLR.DS == 1时,LPI始终是Group 1中断。

系统寄存器控制和配置Group 0和Group 1中断:

-

对于Group 0中断,软件使用:

-

ICC_IAR0_EL1在中断确认时读取Group 0 INTID。

-

ICC_EOIR0_EL1写入Group 0中断完成。

-

ICC_BPR0_EL1配置Group 0优先级的binary point。当ICC_CTLR_EL1.CBPR == 1时,此寄存器也用于Group 1优先级。

-

ICC_HPPIR0_EL1读取当前挂起的最高Group 0中断。

-

ICC_IGRPEN0_EL1在CPU interface启用Group 0中断。

-

-

对于Group 1中断,软件使用:

-

ICC_IAR1_EL1在中断确认时读取Group 1 INTID。

-

ICC_EOIR1_EL1写入Group 1中断完成。

-

ICC_BPR1_EL1为当前Security状态配置Group 1优先级的binary point。

-

ICC_HPPIR1_EL1读取当前挂起的最高Group 1中断。

-

ICC_IGRPEN1_EL1为中断的目标Security状态启用Group 1中断。

-

在具有两个Security状态的系统中,Group 0中断始终是Secure的。有关分组和Security的更多信息,参见_中断分组和安全性_。

4.6.1 中断分组和安全性

Arm架构提供两个Security状态,每个状态都有相关的物理内存地址空间:

-

Secure状态。

-

Non-secure状态。

用户和特权代码的软件层次结构可以在任一状态执行,在Non-secure状态执行的软件只能通过对Secure monitor的系统调用访问Secure状态。GIC架构支持与两个Security状态相关的中断的路由和处理。

GICD_CTLR.DS指示GIC是否配置为支持Armv8-A Security模型。此配置影响:

-

寄存器访问,参见_GIC系统寄存器访问_。

-

支持的中断组。

当GICD_CTLR.DS == 0时:

-

GIC支持两个Security状态,Secure状态和Non-secure状态。

-

GIC支持三个中断组:

- Group 0。 - Secure Group 1。- Non-secure Group 1。

-

Security状态和GICR_NSACR都确定是否可以生成SGI。

-

在以下期间检查Security状态:

- 中断配置。 - 中断确认。-

优先级下降。

-

去激活。

-

-

如果满足以下条件,Secure Group 1中断被CPU interface视为Group 0:

-

PE未实现EL3。

-

ICC_SRE_EL1(S).SRE == 0。

-

当GICD_CTLR.DS == 1时:

-

GIC仅支持单个Security状态。这可以是Secure状态或Non-secure状态。

-

GIC支持两个中断组:

-

Group 0。

-

Group 1。

-

-

无论GICR_NSACR中的设置如何,都可以生成SGI。

-

在以下期间不检查Security状态:

-

中断配置。

-

中断确认。

-

优先级下降。

-

-

去激活。

在多处理器系统中,系统内的一个或多个PE可能支持访问仅在Secure状态可用的资源,或访问仅在Non-secure状态可用的资源。如果软件配置以下情况,这是编程错误:

-

Group 0或Secure Group1中断转发到仅支持Non-secure状态的PE。

-

Non-secure Group1中断转发到仅支持Secure状态的PE。

每个中断组都有专用的优先级分组寄存器,Group 0中断的ICC_BPR0_EL1和Group 1中断的ICC_BPR1_EL1。但是,可以使用以下方法为两个组配置通用Binary Point Register:

-

ICC_CTLR_EL1.CBPR。

-

ICC_CTLR_EL3.CBPR_EL1NS和ICC_CTLR_EL3.CBPR_EL1S用于Non-secure Group 1和Secure Group 1中断的独立通用Binary Point Register配置。

有关中断分组和legacy operation的信息,参见第14章_Legacy Operation和不对称配置_。

4.6.2 中断分配到IRQ和FIQ信号

本小节适用于启用亲和性路由的实现。

Group 0物理中断,当它是最高优先级挂起中断并具有足够优先级时,始终作为FIQ发送信号。

Group 1物理中断,当它是最高优先级挂起中断并具有足够优先级时,如果以下任一条件为真,则作为FIQ发送信号,否则作为IRQ发送信号:

-

它是另一个Security状态的中断,即PE未执行的Security状态。

-

PE在EL3执行。

表4-3总结了EL3使用AArch64状态时的中断信号发送。

表4-3 EL3使用AArch64状态时两个Security状态的中断信号

| 当前Exception level | Group 0中断 | Secure Group 1中断 | Non-secure Group 1中断 |

|---|---|---|---|

| Secure EL1或EL0或EL2 | FIQ | IRQ | FIQ |

| Non-secure EL1或EL0,或Non-secure EL2 | FIQ | FIQ | IRQ |

| EL3 | FIQ | FIQ | FIQ |

表4-4总结了EL3使用AArch32状态时的中断信号发送。当EL3使用AArch32状态时,Secure EL2不存在。

表4-4 EL3使用AArch32状态时两个Security状态的中断信号

| 当前Exception level | Group 0中断 | Secure Group 1中断 | Non-secure Group 1中断 |

|---|---|---|---|

| Secure EL0 | FIQ | IRQ | FIQ |

| Non-secure EL1或EL0,或Non-secure EL2 | FIQ | FIQ | IRQ |

| EL3 | FIQ | IRQ | FIQ |

表4-5总结了仅支持单个Security状态的系统中的中断信号发送,即未实现EL3或GICD_CTLR.DS == 1。

表4-5 单个Security状态的中断信号

| 当前Exception level | Group 0中断 | Group 1中断 |

|---|---|---|

| 任意 | FIQ | IRQ |

IRQ和FIQ的断言和去断言受PE的当前Exception level和Security状态影响。作为由于接受或从异常返回而发生的Context Synchronization的一部分,CPU interface确保IRQ和FIQ都适当地为PE进入的Exception level和Security状态断言或去断言。

注意 有关GICC_CTLR.FIQEn对不对称配置中中断信号发送的影响,参见_不对称配置_。

4.6.3 中断路由和系统寄存器访问

在AArch64状态执行时,到Exception level的中断路由由以下位控制:

-

SCR_EL3.FIQ、SCR_EL3.NS和HCR_EL2.FMO控制FIQ。

-

SCR_EL3.IRQ、SCR_EL3.NS和HCR_EL2.IMO控制IRQ。

此路由还控制控制和确认中断的EL1 CPU interface系统寄存器可访问的Exception level。这适用于:

-

ICC_IAR0_EL1、ICC_EOIR0_EL1、ICC_HPPIR0_EL1、ICC_BPR0_EL1、ICC_AP0R

_EL1和ICC_IGRPEN0_EL1。这些是与Group 0中断相关的寄存器。 -

ICC_IAR1_EL1、ICC_EOIR1_EL1、ICC_HPPIR1_EL1、ICC_BPR1_EL1、ICC_AP1R

_EL1和ICC_IGRPEN1_EL1。这些是与Group 1中断相关的寄存器。 -

ICC_SGI0R_EL1、ICC_SGI1R_EL1、ICC_ASGI1R_EL1、ICC_CTLR_EL1、ICC_DIR_EL1、ICC_PMR_EL1和ICC_RPR_EL1。这些是通用寄存器。

当(SCR_EL3.NS == 1 || SCR_EL3.EEL2== 1) && (HCR_EL2.FMO ==1 || HCR_EL2.IMO == 1))时,EL1的访问是虚拟访问。对ICC_SGI0R_EL1、ICC_SGI1R_EL1和ICC_ASGI1R_EL1的虚拟访问始终生成被接受到EL2的Trap异常。

当Distributor支持两个Security状态时,PE可能不实现EL2或EL3。表4-6显示了这些情况下支持的配置。

表4-6 未实现EL3时支持的配置

| Distributor | EL3 | EL2 | Security状态 | 描述 |

|---|---|---|---|---|

| 两个Security状态,GICD_CTLR.DS == 0 | 否 | - | Non-secure | PE始终是Non-secure,只能接收Non-secure Group 1中断。PE必须表现为软件已经:将ICC_SRE_EL3.Enable设置为1;将ICC_SRE_EL3.DFB设置为1;将SCR_EL3.FIQ设置为1;将SCR_EL3.IRQ清除为0;将SCR_EL3.NS设置为1;将ICC_IGRPEN0_EL1.Enable清除为0;将ICC_IGRPEN1_EL1.Enable的Secure副本设置为0。 |

| 两个Security状态,GICD_CTLR.DS == 0 | 否 | 否 | Secure | PE始终是Secure,只能接收Group 0和Secure Group 1中断。PE必须表现为软件已经:将ICC_SRE_EL3.Enable设置为1;将SCR_EL3.FIQ清除为0;将SCR_EL3.IRQ清除为0;将SCR_EL3.NS清除为0;将ICC_IGRPEN1_EL1.Enable的Non-secure副本清除为0。 |

| 一个Security状态,或两个Security状态且GICD_CTLR.DS == 1 | 否 | - | - | Distributor和所有PE始终在单个Security状态,可以接收Group 0和Group 1中断。所有PE必须表现为软件已经:将ICC_SRE_EL3.Enable设置为1;将SCR_EL3.FIQ清除为0;将SCR_EL3.IRQ清除为0;将SCR_EL3.NS设置为1。 |

4.7 启用中断分发

以下控制位启用和禁用中断分发:

-

GICD_CTLR.EnableGrp1S。

-

GICD_CTLR.EnableGrp1NS。

-

GICD_CTLR.EnableGrp0。

以下控制位在CPU interface启用和禁用中断组的分发:

-

ICC_IGRPEN0_EL1.Enable用于Group 0中断。

-

ICC_IGRPEN1_EL1.Enable用于Group 1中断。

注意

-

此寄存器有Secure和Non-secure副本。

-

ICC_IGRPEN1_EL3.{EnableGrp1S, EnableGrp1NS}。

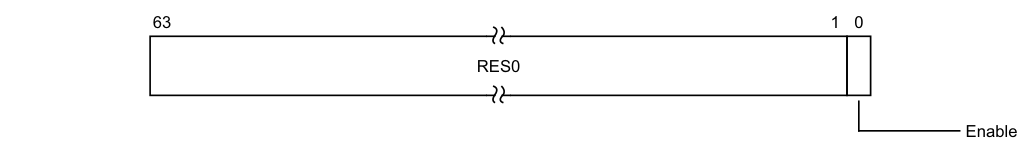

通过写入GICR_CTLR.EnableLPIs启用物理LPI。

4.7.1 启用单个中断

PPI

当为中断的Security状态启用亲和性路由时,可以通过写入GICR_ISENABLER0和GICR_ICENABLER0启用和禁用PPI。如果支持并配置了物理中断的legacy operation,单个PPI也可以通过写入GICD_ISENABLER

可选扩展PPI范围中的PPI通过写入GICR_ISENABLER

SPI

单个SPI可以通过写入GICD_ISENABLER

可选扩展SPI范围中的SPI通过写入GICD_ISENABLER

SGI

当启用亲和性路由时,SGI可以通过写入GICR_ISENABLER0和GICR_ICENABLER0启用和禁用。如果支持并配置了物理中断的legacy operation,单个SGI也可以通过写入GICD_ISENABLER

注意 SGI是永久启用的,还是可以通过写入GICR_ISENABLER0和GICR_ICENABLER0启用和禁用,是IMPLEMENTATION DEFINED。

LPI

单个LPI可以通过设置LPI Configuration表中编程的启用位来启用。有关使用LPI Configuration表启用LPI的更多信息,参见_LPI配置表_。

4.7.2 组和单个中断启用的交互

GICD_*和GICR_*寄存器在任何时刻确定硬件为每个目标PE知晓的最高优先级挂起中断。此中断呈现给PE的CPU interface以评估是否向PE发送信号。中断启用影响此评估如下:

-

在GICD_*或GICR_*寄存器中单独禁用的挂起中断不是确定最高优先级挂起中断时考虑的中断,因此无法向PE发送信号。

-

在GICD_*或GICR_*寄存器中单独启用但在GICD_CTLR中是禁用组成员的挂起中断不是确定最高优先级挂起中断时考虑的中断,因此无法向PE发送信号。

-

在GICD_*寄存器中单独启用且在GICD_CTLR中是启用组成员但在PE的ICC_IGRPEN0_EL1、ICC_IGRPEN1_EL1或ICC_IGRPEN1_EL3中是禁用组成员的挂起1 of N中断无法为该PE选择。这样的中断在确定最高优先级挂起中断时不被考虑,因此无法向PE发送信号。

-

对于在GICD_*或GICR_*寄存器中单独启用且在GICD_CTLR中是启用组成员但在ICC_IGRPEN0_EL1、ICC_IGRPEN1_EL1或ICC_IGRPEN1_EL3中是禁用组成员的挂起直接中断,是否在确定最高优先级挂起中断时考虑该中断是IMPLEMENTATION DEFINED。如果确定为最高优先级挂起中断,中断不向PE发送信号,但将掩码在ICC_IGRPEN0_EL1、ICC_IGRPEN1_EL1或ICC_IGRPEN1_EL3中是启用组成员的较低优先级挂起中断。

LPI在LPI配置表中单独启用,参见_LPI配置表_。

4.7.3 禁用中断的影响

通过写入适当的GICD_ICENABLER

如果GICD_CTLR.EnableGrp0、GICD_CTLR.EnableGrp1S和GICD_CTLR.EnableGrp1NS都清除为0,是否满足以下条件是IMPLEMENTATION DEFINED:

-

边缘触发中断信号将中断移动到挂起状态。

-

通过写入GICD_SGIR、ICC_SGI0R_EL1、ICC_SGI1R_EL1或ICC_ASGI1R_EL1可以设置SGI为挂起。

如果当相应的GICD_CTLR.EnableGrp0、GICD_CTLR.EnableGrp1NS或GICD_CTLR.EnableGrp1S位从1写入0时中断在CPU interface上挂起,则必须从CPU interface检索中断。

注意 如果中断已经被激活,这可能对转发的中断没有影响。

如果当软件将ICC_IGRPEN0_EL1.Enable、ICC_IGRPEN0_EL1、ICC_IGRPEN1_EL1.Enable或ICC_IGRPEN1_EL3.Enable从1写入0时中断在CPU interface上挂起,中断必须由CPU interface释放以允许Distributor将中断转发到不同的PE。

4.8 中断优先级

本节描述GIC架构中的中断优先级。优先级描述:

-

中断优先级的配置和控制。

-

挂起中断的执行顺序。

-

确定中断何时对目标PE可见,包括:

-

中断优先级掩码。

-

优先级分组。

-

活跃中断的抢占。

-

软件通过为每个中断源分配优先级值在GIC中配置中断优先级。优先级值是8位无符号二进制数。支持两个Security状态的GIC实现必须实现最少32个和最多256个物理优先级。仅支持单个Security状态的GIC实现必须实现最少16个和最多256个物理优先级。如果GIC实现少于256个优先级,优先级字段的低位是RAZ/WI。这意味着实现的优先级字段位数是IMPLEMENTATION DEFINED,范围4-8。表4-7显示了优先级字段位与实现支持的优先级数量之间的关系。

表4-7 不实现某些优先级字段位的影响

| 实现的优先级位 | 可能的 | 优先级字段值 | 优先级数量 |

|---|---|---|---|

| [7:0] | 0x00-0xFF | (0-255),所有值 | 256 |

| [7:1] | 0x00-0xFE, | (0-254),仅偶数值 | 128 |

| [7:2] | 0x00-0xFC | (0-252),步长为4 | 64 |

| [7:3] | 0x00-0xF8 | (0-248),步长为8 | 32 |

| [7:4] | 0x00-0xF0 | (0-240),步长为16 | 16 |

在GIC优先级方案中,较小的数字具有较高的优先级。这意味着分配的优先级值越低,中断的优先级越高。优先级字段值0始终指示可能的最高中断优先级,最低优先级值取决于实现的优先级数量。

GICD_IPRIORITYR

在多处理器实现中,GICR_IPRIORITYR

内存中的LPI配置表和LPI挂起表存储LPI优先级信息和挂起状态,参见_LPI配置表_和_LPI挂起表_。

GIC安全模型为中断优先级设置提供Secure和Non-secure访问。Non-secure访问只能在支持的优先级值的较低优先级一半中配置中断。因此,如果GIC实现32个优先级值,Non-secure访问只看到16个优先级值。参见_中断优先级的软件访问_获取更多信息。

要确定SPI实现的优先级位数,软件可以向可写的GICD_IPRIORITYR

要确定SGI和PPI实现的优先级位数,软件可以向GICR_IPRIORITYR

GIC架构不要求系统中的所有PE使用相同数量的优先级位来控制中断优先级。

在多处理器实现中,ICC_CTLR_EL1.PRIbits和ICC_CTLR_EL3.PRIbits为每个目标PE独立指示实现的优先级位数。

注意 Arm建议实现为每个PE支持相同数量的优先级位。

有关虚拟中断支持的优先级范围的信息,参见第6章_虚拟中断处理和优先级_。

注意 Arm建议在以这种方式检查优先级范围之前:

-

对于外设中断,软件首先禁用中断。

-

对于SGI,软件首先检查中断是非活跃的。

如果在特定CPU interface上,多个挂起中断具有相同优先级,并且具有足够优先级供interface向PE发送信号,interface如何选择向哪个中断发送信号是IMPLEMENTATION DEFINED。

GICv3保证最高优先级、未掩码、启用的中断将在有限时间内投递到目标PE。

不保证较高优先级中断总是在较低优先级中断之前获取,尽管这通常是这种情况。

本节的其余部分描述:

-

对Secure中断优先级寄存器字段的Non-secure访问。

-

优先级分组。

-

对Active Priorities寄存器的系统寄存器访问。

-

抢占。

-

优先级掩码。

-

中断优先级的软件访问。

-

更改启用的PPI、SGI和SPI的优先级。

4.8.1 对Secure中断优先级寄存器字段的Non-secure访问

当GICD_CTLR.DS == 0时,GIC支持使用:

-

Group 0中断作为Secure中断。

-

Secure Group 1中断。

-

Non-secure Group 1中断。

为了支持Armv8 Security模型,与Secure中断相关的寄存器字段对Non-secure访问是RAZ/WI。此外,以下规则适用:

对GICx_IPRIORITYR中优先级字段的Non-secure访问:

如果优先级字段对应于_中断优先级的软件访问_中的Non-secure Group 1中断:

-

对于SPI,优先级字段由GICD_IPRIORITYR

或GICD_IPRIORITYR E确定。 -

对于PPI和SGI,优先级字段由GICR_IPRIORITYR

或GICR_IPRIORITYR E确定。

当SCR_EL3.FIQ == 1时对ICC_PMR_EL1和ICC_RPR_EL1的Non-secure访问:

-

如果当前优先级掩码值在0x00-0x7F范围内:

- 读访问返回值0x00。

-

GIC忽略对ICC_PMR_EL1的写访问。

-

如果当前优先级掩码值在0x80-0xFF范围内:

-

读访问返回当前值的Non-secure读取。

-

基于写入寄存器的优先级掩码值的Non-secure读取,对ICC_PMR_EL1的写访问成功。

注意

这意味着Non-secure写入无法在0x00-0x7F范围内设置优先级掩码值。

当SCR_EL3.FIQ == 0时对ICC_PMR_EL1和ICC_RPR_EL1的Non-secure访问:

适用Secure、未移位视图。

_AArch64函数_提供了伪代码,描述了在支持两个Security状态的GIC中对以下系统寄存器的访问:

-

ICC_PMR_EL1。

-

ICC_RPR_EL1。

4.8.2 优先级分组

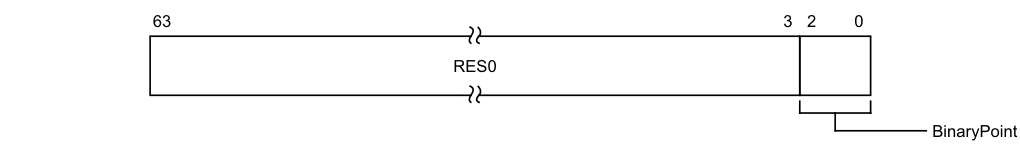

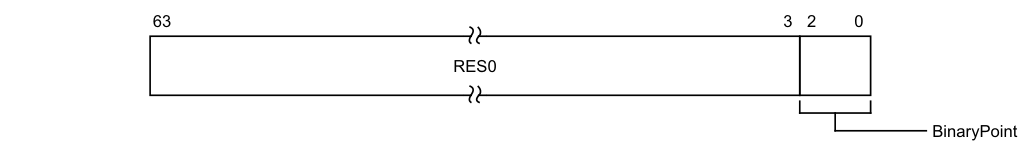

优先级分组使用以下_Binary Point Registers_:

-

ICC_BPR0_EL1用于Group 0中断。此寄存器在所有GIC实现中可用。

-

ICC_BPR1_EL1的Non-secure副本用于Non-secure Group 1中断。如果实现支持两个Security状态,此寄存器有Secure和Non-secure副本。如果实现仅支持一个Security状态,此寄存器只有一个副本。

-

ICC_BPR1_EL1的Secure副本用于Secure Group 1中断。此寄存器仅在支持两个Security状态的GIC实现中可用。

Binary Point Registers将优先级值分为两个字段,组优先级_和_子优先级。在确定抢占时,具有相同组优先级的所有中断被认为具有相同优先级,无论子优先级如何。

当多个挂起中断具有相同组优先级时,GIC使用子优先级字段解决组内的优先级。当一组中有两个或更多挂起中断具有相同子优先级时,GIC如何在中断之间选择是实现特定的。

GIC使用组优先级字段确定挂起中断是否具有足够优先级抢占PE上的执行,如下:

-

中断的组优先级字段值必须低于PE的运行优先级值。运行优先级是该PE上尚未接收到优先级下降的最高优先级活跃中断的组优先级。

-

中断的优先级值必须低于其优先级掩码的值。

ICC_BPR0_EL1确定Group 0中断的优先级分组:

-

当ICC_CTLR_EL3.CBPR_EL1S设置为1时,ICC_BPR0_EL1也确定Secure Group 1中断的优先级分组。

-

当ICC_CTLR_EL3.CBPR_EL1NS设置为1时,ICC_BPR0_EL1也确定Non-secure Group 1中断的优先级分组。

ICC_BPR1_EL1确定Group 1中断的优先级:

-

当ICC_CTLR_EL3.CBPR_EL1S清除为0时,ICC_BPR1_EL1的Secure副本确定Secure Group 1中断的优先级分组。

-

当ICC_CTLR_EL3.CBPR_EL1NS清除为0时,ICC_BPR1_EL1的Non-secure副本确定Non-secure Group 1中断的优先级分组。

表4-8显示了Secure ICC_BPR1_EL1的中断优先级字段分割。

表4-8 当CBPR == 0时的Secure ICC_BPR1_EL1 Binary Point

| ICC_BPR1_EL1 Binary point 值 | 组 优先级字段 | 子优先级字段 | 带binary point的字段 |

|---|---|---|---|

| 0 | [7:1] | [0] | ggggggg.s |

| 1 | [7:2] | [1:0] | gggggg.ss |

| 2 | [7:3] | [2:0] | ggggg.sss |

| 3 | [7:4] | [3:0] | gggg.ssss |

| 4 | [7:5] | [4:0] | ggg.sssss |

| 5 | [7:6] | [5:0] | gg.ssssss |

| 6 | [7] | [6:0] | g.sssssss |

| 7 | 无抢占 | [7:0] | .ssssssss |

表4-9显示了Non-secure ICC_BPR1_EL1的中断优先级字段分割。

表4-9 当CBPR == 0时的Non-secure ICC_BPR1_EL1 Binary Point

| ICC_BPR1_EL1 Binary point 值 | 组 优先级字段 | 子优先级字段 | 带binary point的字段 |

|---|---|---|---|

| 0 | - | - | - |

| 1 | [7:1] | [0] | ggggggg.s |

| 2 | [7:2] | [1:0] | gggggg.ss |

| 3 | [7:3] | [2:0] | ggggg.sss |

| 4 | [7:4] | [3:0] | gggg.ssss |

| 5 | [7:5] | [4:0] | ggg.sssss |

| 6 | [7:6] | [5:0] | gg.ssssss |

| 7 | [7] | [6:0] | g.sssssss |

表4-10显示了ICC_BPR0_EL1的中断优先级字段分割。

表4-10 当CBPR == 1时Group 1中断或Group 0中断的ICC_BPR0_EL1 Binary Point

| Binary point值 | 组优先级字段 | 子优先级字段 | 带binary point的字段 |

|---|---|---|---|

| 0 | [7:1]ᵃ | [0] | ggggggg.s |

| 1 | [7:2]ᵃ | [1:0] | gggggg.ss |

| 2 | [7:3]ᵃ | [2:0] | ggggg.sss |

| 3 | [7:4]ᵃ | [3:0] | gggg.ssss |

| 4 | [7:5]ᵃ | [4:0] | ggg.sssss |

| 5 | [7:6]ᵃ | [5:0] | gg.ssssss |

| 6 | [7]ᵃ | [6:0] | g.sssssss |

| 7 | 无抢占 | [7:0] | .ssssssss |

a. 如果Non-secure写入为Non-secure中断设置优先级值字段,则bit[7] == 1。

支持的最小binary point值取决于IMPLEMENTATION DEFINED的优先级位数,如表4-11所示。

表4-11 最小binary point值支持

| 实现的优先级位数 | ICC_BPR0_EL1的最小值 |

|---|---|

| 8 | 0 |

| 7 | 0 |

| 6 | 1 |

| 5 | 2 |

| 4 | 3 |

实现的优先级位数由ICC_CTLR_EL1.PRIBits和ICC_CTLR_EL3.PRIBits指示。

在支持两个Security状态的GIC中,当:

-

ICC_CTLR_EL3.CBPR_EL1S == 1:

-

在Secure EL1对ICC_BPR1_EL1的写入修改ICC_BPR0_EL1。

-

在Secure EL1从ICC_BPR1_EL1的读取返回ICC_BPR0_EL1的值。

-

-

ICC_CTLR_EL3.CBPR_EL1NS == 1:

-

对ICC_BPR1_EL1的Non-secure写入被忽略。

-

从ICC_BPR1_EL1的Non-secure读取返回ICC_BPR0_EL1 + 1饱和到0b111。

-

注意

-

当中断使用Non-secure ICC_BPR1_EL1时,有效binary point值是存储在寄存器中的值减一,如表4-9所示。这意味着对中断分组影响没有意识且支持两个Security状态的软件,无论它是在Secure状态还是Non-secure状态的PE上运行,都会看到相同的优先级分组机制。

-

优先级分组总是对完整优先级操作,这是Secure读取可见的值。这与Non-secure读取对应于Non-secure中断的优先级值可见的值不同。参见图4-8和图4-9。

-

当EL3使用AArch32且ICC_MCTLR.CBPR_EL1S == 1时,在EL3且不在Monitor模式下对ICC_BPR1的访问访问ICC_BPR0的状态。

伪代码

以下伪代码指示中断的组优先级。

// GroupBits()

// ===========

// Returns the priority group field for the current BPR value for the group

bits(8) GroupBits(bits(8) priority, IntGroup group)

bit cbpr_G1NS = if HaveEL(EL3) then ICC_CTLR_EL3.CBPR_EL1NS else ICC_CTLR_EL1.CBPR;

bit cbpr_G1S = if HaveEL(EL3) then ICC_CTLR_EL3.CBPR_EL1S else '0';

if (group == IntGroup_G0 ||

(group == IntGroup_G1NS && cbpr_G1NS == '1') ||

(group == IntGroup_G1S && cbpr_G1S == '1')) then

bpr = UInt(ICC_BPR0_EL1.BinaryPoint);

elsif group == IntGroup_G1S then

bpr = UInt(ICC_BPR1_EL1S.BinaryPoint);

else

bpr = UInt(ICC_BPR1_EL1NS.BinaryPoint) -1;

mask = Ones(7-bpr):Zeros(bpr+1);

return priority AND mask;

4.8.3 系统寄存器访问Active Priorities寄存器

物理Group 0和Group 1中断访问不同的Active Priorities寄存器,取决于中断组。

对于Group 0中断,这些寄存器是ICC_AP0R

-

如果实现32个或更少的优先级,对ICC_AP0R

_EL1的访问(其中n = 1-3)是UNDEFINED。 -

如果实现超过32个且少于65个优先级,对ICC_AP0R

_EL1的访问(其中n = 2-3)是undefined。

对于Group 1中断,这些寄存器是ICC_AP1R

-

如果实现32个或更少的优先级,对ICC_AP1R

_EL1的访问(其中n = 1-3)是undefined。 -

如果实现超过32个且少于65个优先级,对ICC_AP1R

_EL1的访问(其中n = 2-3)是undefined。

ICC_AP0R

向这些寄存器写入最后读取值或0x00000000以外的任何值都可能导致:

-

原本会抢占执行的中断不抢占执行。

-

原本不会抢占执行的中断抢占执行。

对Non-secure ICC_AP1R

按照除以下顺序外的任何顺序写入这些寄存器都可能导致UNPREDICTABLE行为:

-

ICC_AP0R

_EL1。 -

Secure ICC_AP1R

_EL1。 -

Non-secure ICC_AP1R

_EL1。

注意 在每次写入ICC_AP0R

_EL1、Secure ICC_AP1R _EL1和Non-secure ICC_AP1R _EL1之间不需要ISB。

表4-12显示了ICC_AP0R

表4-12 Group 0 Active Priorities Register实现

| 最小值: | : | 最大 | 数量: | |

|---|---|---|---|---|

| Secure ICC_BPR0_EL1 | Non-secure ICC_BPR1_EL1 | 组 优先级 位 | 抢占 级别 | ICC_AP0Rn实现 |

| 3 | 4 | 4 | 16 | ICC_AP0R |

| 2 | 3 | 5 | 32 | ICC_AP0R |

| 1 | 2 | 6 | 64 | ICC_AP0R |

| 0 | 1 | 7 | 128 | ICC_AP0R |

表4-13显示了ICC_AP1R

表4-13 Group 1 Active Priorities Register实现

| 最小值: | 最大 | 数量: | ||

|---|---|---|---|---|

| Secure ICC_BPR0_EL1 | Non-secure ICC_BPR1_EL1 | 组 优先级 位 | 抢占 级别 | ICC_AP1Rn实现 |

| 3 | 4 | 4 | 16 | ICC_AP1R |

| 2 | 3 | 5 | 32 | ICC_AP1R |

| 1 | 2 | 6 | 64 | ICC_AP1R |

| 0 | 1 | 7 | 128 | ICC_AP1R |

4.8.4 抢占

CPU interface支持在活跃中断完成之前向目标PE发送更高优先级挂起中断的信号。挂起中断仅在以下两个条件都满足时才发送信号:

-

其优先级高于该CPU interface的优先级掩码。参见_优先级掩码_。

-

其组优先级高于CPU interface上的运行优先级。参见_优先级分组_获取更多信息。

抢占在PE接受新中断时发生,并开始处理新中断而不是先前活跃的中断或当前运行的进程。当这发生时,初始活跃中断被称为_被抢占_。

注意 Process State PSTATE中I或F位的值,以及Exception level和软件硬件中的中断路由控制,确定PE是否通过接受中断来响应发送信号的中断。有关更多信息,参见_Arm[®]架构参考手册,Armv8,针对Armv8-A架构配置文件_。

有关启用中断的更多信息,参见_启用中断分发_。

抢占级别控制

ICC_BPR0_EL1确定Group 0中断是否向PE发送信号以进行可能的抢占。此外:

-

当ICC_CTLR_EL3.CBPR_EL1NS == 1时,ICC_BPR0_EL1也确定Non-secure Group 1中断是否向PE发送信号以进行可能的抢占。

-

当ICC_CTLR_EL3.CBPR_EL1S == 1时,ICC_BPR0_EL1也确定Secure Group 1中断是否向PE发送信号以进行可能的抢占。

ICC_BPR1_EL1确定Group 1中断是否向PE发送信号以进行可能的抢占。此寄存器的Non-secure副本用于Non-secure Group 1中断。Secure副本用于Secure Group 1中断。

当ICC_CTLR_EL3.CBPR_EL1NS设置为1时:

-

EL3可以写入ICC_BPR1_EL1(NS)。当EL3使用AArch64状态时,从EL3对ICC_BPR1_EL1(NS)的访问不受ICC_CTLR_EL3.CBPR_EL1NS影响。

- 当EL3使用AArch32状态时,从Monitor模式对ICC_BPR1_EL1(NS)的访问不受ICC_CTLR_EL3.CBPR_EL1NS影响。

-

在EL1或EL2对ICC_BPR1_EL1的Non-secure写入被忽略。

-

在EL1或EL2对ICC_BPR1_EL1的Non-secure读取返回ICC_BPR0_EL1 +1的值,在7处饱和。

当ICC_CTLR_EL3.CBPR_EL1S设置为1时:

-

ICC_BPR1_EL1的Secure读取返回ICC_BPR0_EL1的值。

-

ICC_BPR1_EL1的Secure写入更新ICC_BPR0_EL1。

4.8.5 优先级掩码

CPU interface的_Priority Mask Register_ ICC_PMR_EL1为目标PE定义优先级阈值。GIC仅向目标PE发送具有高于此优先级阈值的优先级的挂起中断信号。零值(寄存器重置值)掩码所有中断向关联PE发送信号。GIC在将挂起中断的优先级与优先级阈值比较时不使用优先级分组。

GIC始终掩码具有最低支持优先级的中断。此优先级有时称为空闲优先级。

注意 向ICC_PMR_EL1写入0xFF总是将其设置为最低支持优先级。表4-7显示了最低支持优先级如何随实现的优先级位数变化。

如果GIC提供两个Security状态的支持,如果bit[7] == 0,ICC_PMR_EL1对Non-secure访问是RAZ/WI。在正常操作期间,在Non-secure状态执行的软件在用这样的值编程时不访问ICC_PMR_EL1。

有关与不同GIC配置相关的信息,参见_对Secure中断优先级寄存器字段的Non-secure访问_。

4.8.6 中断优先级的软件访问

本节描述中断优先级的Secure和Non-secure读取,以及它们之间的关系。它还描述对优先级值字段的写入。

注意 本节适用于任何支持两个Security状态的GIC实现。

当PE读取Non-secure Group 1中断的优先级值时,GIC返回该值的Secure或Non-secure读取,取决于访问是Secure还是Non-secure。

GIC实现最少32个和最多256个优先级。这意味着它实现了适当GICR_IPRIORITYR

| 7 6 5 4 | 7 6 5 4 | 7 6 5 4 | 7 6 5 4 | 3 2 1 0 | 3 2 1 0 | 3 2 1 0 | 3 2 1 0 |

|---|---|---|---|---|---|---|---|

| H | G | F | E | D | C | B | A |

图4-5 任何中断优先级字段的Secure读取

在此视图中:

-

位H-D是GIC必须实现的位,对应32个优先级。

-

位C-A是GIC可能实现的位。如果未实现,它们是RAZ/WI。

-

GIC必须实现位H-A以提供最大256个优先级。

对于Non-secure访问,GIC支持它为Secure访问支持的一半优先级,这意味着最少16个优先级。图4-6显示了Non-secure Group 1中断的优先级值字段的Non-secure视图。

| 7 6 5 4 | 7 6 5 4 | 7 6 5 4 | 7 6 5 4 | 3 2 1 0 | 3 2 1 0 | 3 2 1 0 | 3 2 1 0 |

|---|---|---|---|---|---|---|---|

| G | F | E | D | C | B | A | 0 |

图4-6 Non-secure Group 1中断优先级字段的Non-secure读取

在此读取中:

-

位G-D是GIC必须实现的位,对应16个优先级。

-

位C-A是GIC可能实现的位,如果未实现则是RAZ/WI。

-

GIC必须实现位G-A以提供最大128个优先级。

-

位[0]是RAZ/WI。

优先级值的Non-secure读取不显示值在Distributor的寄存器中如何存储。对于Non-secure Group 1中断优先级字段的Non-secure写入,在存储值之前:

-

值右移一位。

-

值的位[7]设置为1。

此转换意味着Non-secure Group 1中断的优先级值在优先级范围的下半部分。

中断优先级值的Secure读取返回存储在Distributor中的值。图4-7显示了由Non-secure访问设置优先级值字段或由Secure访问设置bit[7] == 1的优先级值的Non-secure Group 1中断的优先级值字段的Secure读取:

| 7 6 5 4 | 7 6 5 4 | 7 6 5 4 | 7 6 5 4 | 3 2 1 0 | 3 2 1 0 | 3 2 1 0 | 3 2 1 0 |

|---|---|---|---|---|---|---|---|

| 1 | G | F | E | D | C | B | A |

图4-7 Non-secure Group 1中断优先级字段的Secure读取

Non-secure Group 1中断优先级值字段的Secure写入可以将位[7]设置为0。如果Secure写入将bit[7]设置为0:

-

Non-secure读取返回值GFEDCBA0。

-

Non-secure写入可以更改字段的值,但只能更改为字段的Secure读取具有位[7]设置为1的值。

注意

-

Non-secure访问的此行为仅适用于GICR_IPRIORITYR

和GICD_IPRIORITYR 中的优先级值字段,适当时: -

如果ICC_PMR_EL1中的Priority字段保存位[7] == 0的值,则该字段对Non-secure访问是RAZ/WI。

-

如果ICC_RPR_EL1中的Priority字段保存位[7] == 0的值,则该字段对Non-secure读取是RAZ。

-

-

Arm不建议以这种方式为Non-secure Group 1中断将bit[7]设置为0,因为它将中断放在错误的优先级范围一半中以供non-secure代码维护。

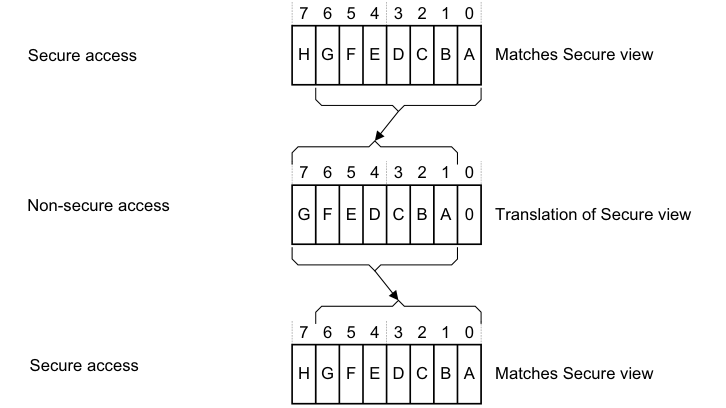

图4-8显示了Non-secure Group 1中断优先级值字段读取之间的关系。

图片文本

7 6 5 4 3 2 1 0

Secure access H G F E D C B A Matches Secure view

7 6 5 4 3 2 1 0

Non-secure access

G F E D C B A 0 Translation of Secure view

7 6 5 4 3 2 1 0

Secure access

H G F E D C B A Matches Secure view

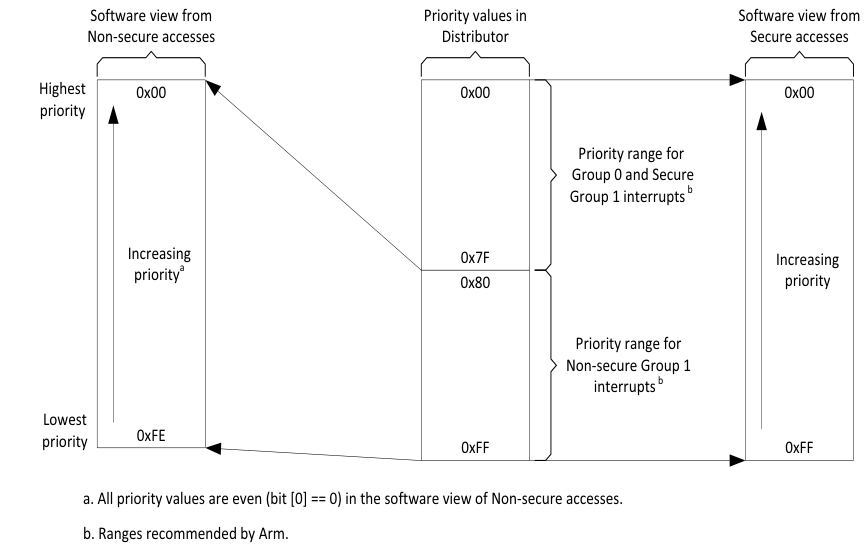

图4-9显示了来自Secure和Non-secure访问的中断优先级的软件读取如何与Distributor中保存的优先级值,以及Secure和Non-secure访问可见的中断值相关。图4-9适用于实现最大优先级值范围的GIC。

图片文本

Software view from Priority values in Software view from

Non-secure accesses Distributor Secure accesses

Highest 0x00 0x00 0x00

priority

Priority range for

Group 0 and Secure

Group 1 interrupts [ b]

Increasing 0x7F Increasing

priority [a] 0x80 priority

Priority range for

Non-secure Group 1

interrupts [ b]

Lowest

0xFE

priority 0xFF 0xFF

a. 在Non-secure访问的软件视图中,所有优先级值都是偶数(bit [0] == 0)。

b. Arm建议的范围。

表4-14显示了GIC实现的优先级值位数如何影响Non-secure Group 1中断优先级的Secure和Non-secure读取。

注意 在Non-secure状态执行的软件无法看到Group 0中断或(如果适用)Secure Group 1中断的优先级设置。

表4-14 不实现某些优先级字段位的影响,两个Security状态

| 由Secure读取看到的实现优先级位 [7:0] | Non-secure Group 1中断的可能优先级字段值 Secure读取 Non-secure读取 | |—|— 0xFF-0x00(255-0),所有值 0xFE-0x00(254-0),仅偶数值 | | [7:1] | 0xFE-0x00(254-0),仅偶数值 0xFC-0x00(252-0),步长为4 | | [7:2] | 0xFC-0x00(252-0),步长为4 0xF8-0x00(248-0),步长为8 | | [7:3] | 0xF8-0x00(248-0),步长为8 0xF0-0x00(240-0),步长为16 |

此优先级值表示模型确保编写为与此GIC架构实现一起操作的软件按预期功能,无论GIC是否提供两个Security状态的支持。但是,程序员必须确保软件为Group 0和Group 1中断分配适当的优先级。

注意 为了控制优先级值,Arm强烈建议:

- 对于Group 0中断,软件将优先级值字段的bit[7]设置为0。

- 如果使用Secure写入设置Non-secure Group 1中断的优先级,软件将优先级值字段的bit[7]设置为1。

这确保所有Group 0和(如果适用)Secure Group 1中断具有比所有Non-secure Group 1中断更高的优先级。但是,系统可能有无法用此方案满足的要求。

表4-15显示了确保以下的示例优先级分配方案:

-

一些Group 0中断具有比任何其他中断更高的优先级。

-

一些Secure Group 1中断具有比任何Non-secure Group 1中断更高的优先级。

表4-15 示例优先级分配

| 中断安全配置 | GICR_IPRIORITYR |

|---|---|

| Group 0 | 0b00 |

| Secure Group 1 | 0b01 |

| Non-secure Group 1 | 0b10 0b11 |

-

软件可能不知道GIC支持两个Security状态,因此可能不知道它是否对GIC寄存器进行Secure或Non-secure访问。但是,对于任何实现的中断,软件可以向相应的GICR_IPRIORITYR

优先级值字段写入0xFF,然后读回存储在字段中的值以确定支持的中断优先级范围。Arm建议在以这种方式检查优先级范围之前: - 对于外设中断,软件首先禁用中断。

-

对于SGI,软件首先检查中断是非活跃的。

4.8.7 更改启用的PPI、SGI和SPI的优先级

如果软件在中断挂起时写入启用中断的GICD_IPRIORITYR

第 5 章:本地性特定外设中断和 ITS

本章描述了_本地性特定外设中断_(LPI)和_中断转换服务_(ITS)。包含以下章节:

-

LPI。

-

中断转换服务。

-

ITS 命令。

-

通用 ITS 伪代码函数。

-

ITS 命令错误编码。

-

ITS 电源管理。

5.1 LPI

本地性特定外设中断(LPI)是边沿触发的基于消息的中断,如果实现了_中断转换服务_(ITS),则可以使用 ITS 将中断路由到特定的 Redistributor 和连接的 PE。GICv3 为 LPI 提供两种类型的支持。LPI 可以通过以下任一方式支持:

-

使用 ITS 将来自设备的 EventID 转换为 LPI INTID。有关 EventID 的更多信息,请参见_中断转换服务_。

-

通过使用 GICR_SETLPIR 直接将 LPI INTID 转发到 Redistributor。

实现必须只支持这些方法中的一种。

注意

在支持 LPI 但不包含 ITS 的实现中,以下寄存器是强制性的:

-

GICR_INVLPIR。

-

GICR_INVALLR。

-

GICR_SYNCR。

在确实包含 ITS 的实现中,对这些寄存器的支持是 IMPLEMENTATION DEFINED 的。

这些寄存器控制不包含 ITS 的系统中的物理 LPI:

-

GICR_SETLPIR。

-

GICR_CLRLPIR。

在包含 LPI 的实现中,至少支持 8192 个 LPI。因此,每个中断的配置和每个中断的挂起信息保存在内存中的表中,而不是寄存器中,这些表由保存在 Redistributor 中的寄存器指向。

注意

-

Arm 期望实现将在 Redistributor 中缓存表的部分内容,以减少延迟和内存流量。这些缓存的形式是 IMPLEMENTATION DEFINED 的。

-

LPI 表的地址在 Non-secure 物理地址空间中。

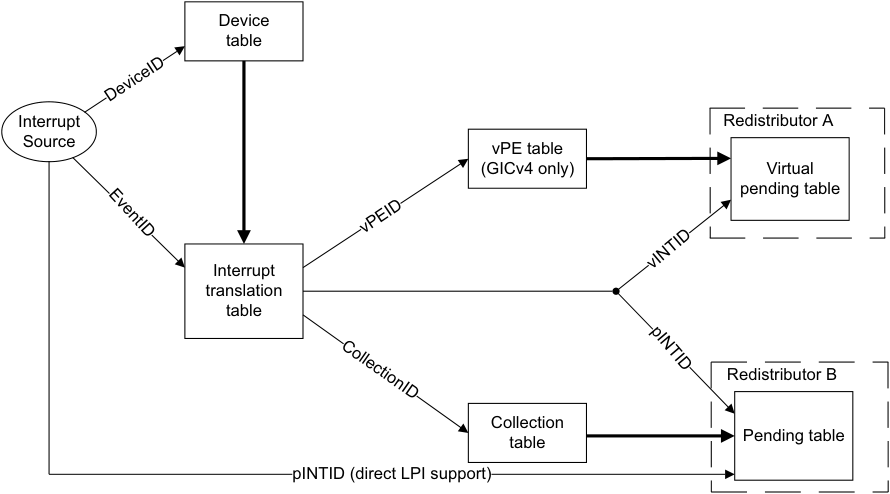

图 5-1 显示了在包含至少一个 ITS 的实现中 LPI 的生成。

Image text

Message-based interrupts

Distributor ITS [a]

GITS_TRANSLATER

LPIs

PE PE PE PE PE

x.y.0.0 x.y.0.1 x.y.0.2 x.y.n.0 x.y.n.1

Cluster C0 Cluster Cn

Redistributor CPU interface

图 5-1 在带有 ITS 的实现中触发 LPI

注意 在图 5-1 中,ITS 到 Redistributor 的通道是 IMPLEMENTATION DEFINED 的。

图 5-2 显示了在没有 ITS 的实现中 LPI 的生成。 5.1 LPI

Message-based interrupts

Image text

Distributor

LPIs

PE PE PE PE PE

x.y.0.0 x.y.0.1 x.y.0.2 x.y.n.0 x.y.n.1

Cluster C0 Cluster Cn

Redistributor CPU interface

-

只有在为 Non-secure 状态启用亲和性路由时才支持 LPI。

-

LPI 总是 Non-secure Group 1 中断。

当 GICD_CTLR.DS == 1 时:

-

只有在启用亲和性路由时才支持 LPI。

-

LPI 总是 Group 1 中断。

有一个单一的全局物理 LPI 空间,以便 LPI 可以在所有 Redistributor 之间移动。软件使用 GICR_PROPBASER.IDbits 编程单一全局物理 LPI 空间的大小。

注意 物理 LPI 空间的大小受实现支持的最大大小限制,该大小在 GICD_TYPER.IDbits 中定义。

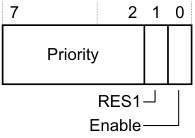

对于给定的 Redistributor,LPI 配置和状态在内存中的两个表中维护,在以下章节中描述:

-

LPI Configuration 表。

-

LPI Pending 表。 如果 Redistributor 支持物理 LPI,它具有:

-

在 LPI Configuration 表中编程的 LPI 优先级和使能位。LPI Configuration 表的地址由 GICR_PROPBASER 定义。如果在 GICR_CTLR.EnableLPIs == 1 时更新 GICR_PROPBASER,效果是 UNPREDICTABLE 的。有关更多信息,请参见_LPI Configuration 表_。

-

LPI Pending 表中 LPI 挂起位的内存支持存储。此表特定于特定的 Redistributor。LPI Pending 表的地址由 GICR_PENDBASER 定义。如果在 GICR_CTLR.EnableLPIs == 1 时更新 GICR_PENDBASER,效果是 UNPREDICTABLE 的。

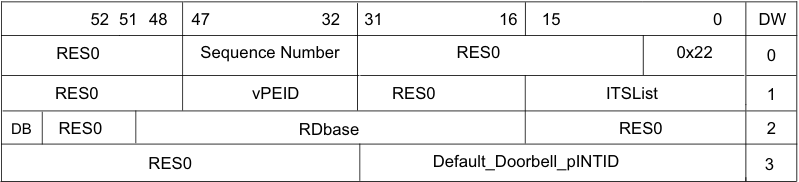

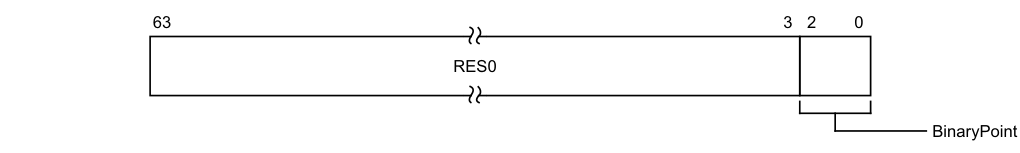

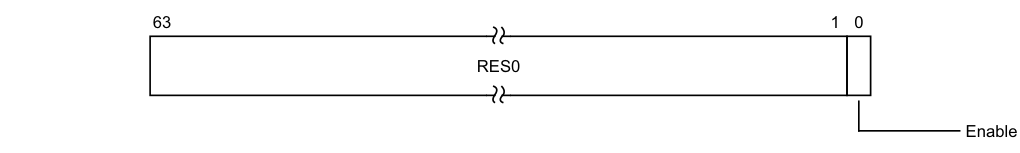

GICR_PROPBASER.IDBits 设置 ID 空间的大小,从而设置 LPI Configuration 表和相应 LPI Pending 表中的条目数量。