第12章:程序员模型

本章提供了有关GIC寄存器接口的信息,并描述了所有的GIC寄存器。它包含以下章节:

-

关于程序员模型。

-

AArch64系统寄存器描述。

-

AArch64虚拟寄存器的系统寄存器描述。

-

AArch64虚拟化控制系统寄存器。

-

AArch32系统寄存器描述。

-

AArch32虚拟寄存器的系统寄存器描述。

-

AArch32虚拟化控制系统寄存器。

-

GIC Distributor寄存器映射表。

-

GIC Distributor寄存器描述。

-

GIC Redistributor寄存器映射表。

-

GIC Redistributor寄存器描述。

-

GIC CPU interface寄存器映射表。

-

GIC CPU interface寄存器描述。

-

GIC virtual CPU interface寄存器映射表。

-

GIC virtual CPU interface寄存器描述。

-

GIC virtual interface control寄存器映射表。

-

GIC virtual interface control寄存器描述。

-

ITS寄存器映射表。

-

ITS寄存器描述。

-

伪代码。

12.1 关于程序员模型

GIC被分割为几个逻辑组件,如第3章_GIC分区_中定义的,每个组件支持一个或多个编程接口。软件使用这些编程接口来访问程序员模型并控制GIC。这些接口要么是内存映射的,要么支持系统寄存器访问,如下所示:

-

Distributor、Redistributor和ITS编程接口总是内存映射的。

-

用于物理和虚拟中断处理的CPU接口,以及hypervisor使用的虚拟机控制接口使用:

-

用于GICv3和GICv4操作的系统寄存器接口。

-

用于legacy操作的内存映射接口。

注意 对legacy操作的支持是可选的。实现允许仅对虚拟中断支持legacy操作,这意味着GICV_*寄存器是唯一提供的内存映射CPU接口寄存器。在这些实现中,不提供GICC_*寄存器和GICH_*寄存器。GICC_*和GICH_*寄存器仅在物理中断支持legacy操作时才需要。

当访问系统寄存器时,访问的寄存器内容取决于:

-

PE正在执行的异常级别。

-

访问是Secure还是Non-secure。

-

对于EL1的Non-secure访问,在AArch64状态下执行时是否由HCR_EL2配置异常级别,或在AArch32状态下执行时是否由HCR配置,以处理虚拟或物理中断。

12.1.1 GIC寄存器名称

所有的GIC寄存器都有提供寄存器功能简短助记符的名称:

-

内存映射寄存器以以下之一为前缀:

- GICC,表示CPU interface寄存器。 - GICD,表示Distributor寄存器。-

GICH,表示virtual interface control寄存器,通常由hypervisor访问。

-

GICR,表示Redistributor寄存器。

-

GICV,表示virtual CPU interface寄存器。

-

GITS,表示ITS寄存器。

-

-

系统寄存器以以下为前缀:

- ICC,表示物理GIC CPU interface系统寄存器。-

ICV,表示虚拟GIC CPU interface系统寄存器。

-

ICH,表示virtual interface control系统寄存器。

-

-

其余字母是寄存器的助记符,例如GIC Distributor Control Register称为GICD_CTLR。

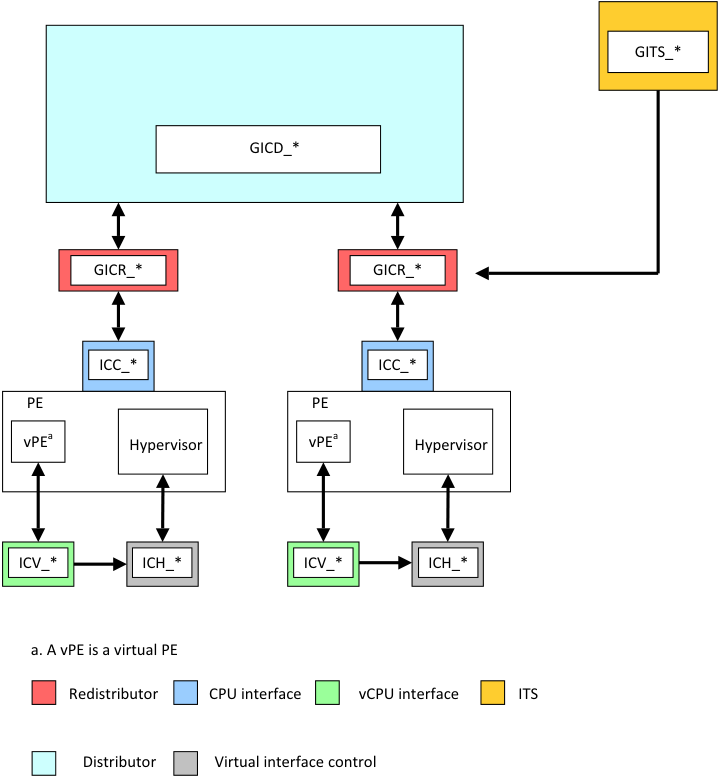

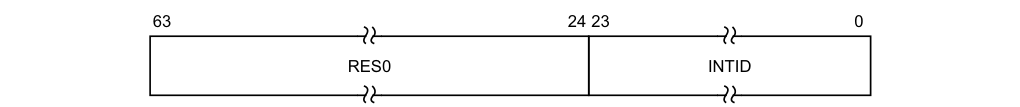

图12-1显示了当所有异常级别启用亲和路由和系统寄存器访问时,程序员可以用于不同逻辑组件的接口。

Image text

GITS_

GICD_

GICR_* GICR_

ICC_ ICC_

PE PE

vPE [a] Hypervisor vPE [a] Hypervisor

ICV_ ICH_* ICV_* ICH_*

a. A vPE is a virtual PE

Redistributor CPU interface vCPU interface ITS

Distributor Virtual interface control

系统寄存器可能可以从不同的异常级别访问。在AArch64状态下,寄存器后缀定义了寄存器可访问的最低异常级别。也就是说,对ICC_*_ELx的任何访问必须来自异常级别ELx或更高。

12.1.2 系统寄存器与内存映射寄存器之间的关系

GIC架构允许但不要求相同的寄存器可以在内存映射寄存器和等效的系统寄存器之间共享。这意味着如果在ICC_SRE_ELx.SRE == 0时访问了内存映射寄存器,系统寄存器可能会被修改。因此,Arm建议软件仅在使用内存映射寄存器时没有使用GIC功能的情况下依赖系统寄存器的复位值,否则Arm建议将这些值视为UNKNOWN。 表12-1显示了在内存映射寄存器和系统寄存器之间共享的寄存器。

表12-1 系统寄存器与内存映射寄存器之间的关系

| 系统寄存器a AArch64 | 内存映射CPU interface寄存器 AArch32 | 内存映射virtual CPU interface寄存器 |

|---|---|---|

| ICC_AP0R | ICC_AP0R | GICV_APR |

| ICC_BPR0_EL1 | ICC_BPR0 GICC_BPR,GICC_ABPRbc ICC_BPR1 | GICV_BPR |

| ICC_BPR1_EL1 | GICV_ABPR | |

| ICC_CTLR_EL1 ICC_CTLR_EL3 | ICC_CTLR GICC_CTLR ICC_MCTLR | GICV_CTLR |

| ICC_DIR_EL1 | ICC_DIR GICC_DIR | GICV_DIR |

| ICC_EOIR0_EL1 | ICC_EOIR0 GICC_EOIR,GICC_AEOIR ICC_EOIR1 | GICV_EOIR |

| ICC_EOIR1_EL1 | GICV_AEOIR | |

| ICC_HPPIR0_EL1 | ICC_HPPIR0 GICC_HPPIR,GICC_AHPPIR ICC_HPPIR1 | GICV_HPPIR |

| ICC_HPPIR1_EL1 | GICV_AHPPIR | |

| ICC_IAR0_EL1 | ICC_IAR0 GICC_IAR,GICC_AIARd ICC_IAR0 | GICV_IAR |

| ICC_IAR1_EL1 | GICV_AIAR | |

| ICC_IGRPEN0_EL1 ICC_IGRPEN1_EL1 ICC_IGRPEN1_EL3 | ICC_IGRPEN0 GICC_CTLR ICC_IGRPEN1 ICC_MGRPEN1 | GICV_CTLR |

| ICC_PMR_EL1 | ICC_PMR GICC_PMR | GICV_PMR |

| ICC_RPR_EL1 | ICC_RPR GICC_RPR | GICV_RPR |

| ICH_AP0R | ICH_AP0R | - |

| ICH_AP1R | - | |

| ICH_EISR_EL2 | ICH_EISR GICH_EISR | - |

| ICH_ELRSR_EL2 | ICH_ELRSR GICH_ELRSR | - |

| ICH_HCR_EL2 | ICH_HCR GICH_HCR | - |

| ICH_LR | ICH_LR | - |

| - | ||

| ICH_MISR_EL2 | ICH_MISR GICH_MISR | - |

| ICH_VMCR_EL2 | ICH_VMCR GICH_VMCR | - |

| ICH_VTR_EL2 | ICH_VTR GICH_VTR | - |

-

a. 还有以ICV而不是ICC为前缀的系统寄存器,这些是虚拟GIC CPU interface系统寄存器,见_AArch64虚拟寄存器的系统寄存器描述_和_AArch32虚拟寄存器的系统寄存器描述_。

-

b. 该寄存器是GICC_BPR的Non-secure副本的别名。

-

c. 如果ICC_CTLR_EL3.CBPR_EL1NS == 1,对该寄存器的Secure访问会访问(并可能修改)ICC_BPR0_EL1。

-

d. 在支持两种安全状态的GIC实现中,该寄存器是GICC_IAR的Non-secure视图的别名。

12.1.3 GIC内存映射寄存器访问

在任何系统中,必须支持对以下寄存器的访问:

-

对以下寄存器的单副本原子32位访问:

- 所有32位GICC_、GICV_、GICD_、GICH_、GITS_*和GICR_*寄存器。

-

对以下寄存器的单副本原子64位访问:

-

所有64位GITS_*寄存器。

-

所有64位GICD_*寄存器。

-

所有64位GICR_*寄存器。

-

-

对以下寄存器的字节访问:

-

GICD_IPRIORITYR

。 -

GICD_ITARGETSR

。 -

GICD_SPENDSGIR

。 -

GICD_CPENDSGIR

。 -

GICR_IPRIORITYR

。

-

此外,在一个或多个PE支持AArch32的系统中:

-

对以下寄存器的单副本原子32位访问:

- 所有64位GICD_*、GICR_*和GITS_*寄存器,包括对寄存器高32位和低32位的独立访问。这不适用于专门标记为仅64位可访问的寄存器。

Arm不期望软件直接访问以下寄存器,但必须支持对这些寄存器的单副本原子16位和32位访问:

-

GITS_TRANSLATER。

-

GICD_SETSPI_NSR。

-

GICD_CLRSPI_NSR。

-

GICD_SETSPI_SR。

-

GICD_CLRSPI_SR。

对这些寄存器的所有其他访问导致UNPREDICTABLE行为。

在GIC架构中,所有可双字访问、半字访问或字节访问的寄存器都使用小端内存顺序模型。

不支持以下访问:

-

除本节中特别列出的寄存器外,对其他寄存器的字节访问。

-

未对齐的字访问。这些访问不是字单副本原子的。

-

未对齐的双字访问。这些访问不是双字单副本原子的。

-

对标记为需要64位访问的寄存器的字访问。

-

除本节中特别列出的双字访问外的其他双字访问。

-

四字或更高。

-

独占访问。

对于这些访问类型中的每一种,以下情况是UNPREDICTABLE的:

-

访问是否生成外部终止。

-

读取的定义副作用是否发生。读取返回UNKNOWN数据。

-

写入是否被忽略或将被访问的寄存器设置为UNKNOWN值。

对于遵循Arm架构的PE的内存映射访问,指令的单副本原子规则、指令类型和访问的内存类型决定了指令进行访问的大小。示例12-1展示了这一点。

示例12-1 内存映射访问的访问大小

对连续双字对齐位置进行的两次Load Doubleword指令生成一对单副本原子双字读取。但是,如果访问是对Normal内存或Device-GRE内存进行的,它们可能表现为外设不支持的单个四字访问。

Armv8不要求内存系统能够在PE之外识别多寄存器加载或存储指令访问的每个元素的大小。任何对GIC的内存映射访问都被定义为在PE之外。

软件必须使用Device-nGRE或更强的内存类型,并且只使用单寄存器加载和存储指令,以创建外设支持的内存访问。

内存映射寄存器的读写按照它们到达GIC的顺序完成。对于访问不同的寄存器位置,软件必须通过以下方式创建此顺序:

-

将内存标记为Device-nGnRnE或Device-nGnRE。

-

使用适当的内存屏障。

软件必须能够保证写入的完成,例如通过:

-

如果系统支持此属性,将内存标记为Device-nGnRnE并执行DSB屏障。

-

读回写入的值。

有关字节序、内存顺序和屏障指令的更多信息,请参阅_Arm[®] Architecture Reference Manual, Armv8, for Armv8-A architecture profile._

内存映射寄存器接口的访问类型定义是:

RW 读写。RO 只读。写入被忽略。WO 只写。读取返回UNKNOWN值。

12.1.4 当系统寄存器访问启用时对内存映射寄存器的访问

因为内存映射访问和系统寄存器访问可能不访问相同的状态,并且当为特定异常级别和安全状态启用系统寄存器访问时不保证同步,Arm建议使用系统寄存器而不是提供相同功能的内存映射寄存器。

在包含GICC_*寄存器的实现中,以及ICC_SRE_EL1.SRE的Secure副本可编程的地方,必须在系统寄存器访问和内存映射访问之间共享以下状态以确保抢占的正确操作:

-

GICC_PMR和ICC_PMR_EL1或ICC_PMR必须访问相同的状态。

-

GICC_APR

和ICC_AP0R _EL1必须访问相同的状态。 -

GICC_NSAPR

和ICC_AP1R _EL1(NS)必须访问相同的状态。 -

GICC_CTLR.CBPR和ICC_CTLR_EL3(NS).CBPR必须访问相同的状态。

-

当GICC_CTLR.CBPR == 0时,对GICC_BPR的Secure访问和ICC_BPR0_EL1必须访问相同的状态。

-

当GICC_CTLR.CBPR == 0时,对GICC_ABPR的Secure访问和ICC_BPR1_EL1必须访问相同的状态。

注意

-

当更改SRE字段的设置时,软件必须遵循_GIC系统寄存器访问_中指定的规则。

-

_系统寄存器与内存映射寄存器之间的关系_指定了内存映射寄存器和系统寄存器之间的关系。状态只能在执行相同功能的寄存器之间共享,表12-1中列出的寄存器可能共享状态。

当从要求寄存器访问相同状态的状态更改为不要求寄存器访问相同状态的状态时,或者当从不要求寄存器访问相同状态的状态更改为要求寄存器访问相同状态的状态时,寄存器的内容变为UNKNOWN。

注意 为内存映射和系统寄存器状态实现的优先级位必须相同,Group 0中断的Binary Point Register的最小值对于Secure和Non-secure视图也必须相同。

对GICC_*寄存器的访问可能受到系统寄存器访问是否启用的影响,这取决于实现:

- 如果ICC_SRE_EL1.SRE的Secure副本== 1,则GICC_*寄存器可能不可访问或可能是RAZ/WI。

注意

当EL3配置为使用AArch32状态时,Secure EL1不可访问,但软件仍必须将ICC_SRE.SRE的Secure副本设置为1,以启用对Secure Group 1中断的支持,否则系统是UNPREDICTABLE的。

-

如果ICC_SRE_EL2.SRE == 1,则GICH_*寄存器可能不可访问或可能是RAZ/WI。

-

如果ICC_SRE_EL1.SRE的Non-secure副本== 1,则GICV_*寄存器可能不可访问或可能是RAZ/WI。

注意 在ICC_SRE_EL1.SRE的Non-secure副本可编程的实现中,即它不是RAO/WI,仍必须提供GICV_*寄存器接口。

实现可能能够检测到由于SRE位为1而不能访问的内存映射寄存器的访问,并以IMPLEMENTATION DEFINED的方式报告它们。

12.1.5 执行状态

Armv8-A架构有两种执行状态:

-

AArch64状态。

-

AArch32状态。

要查看AArch64系统寄存器和AArch32系统寄存器之间的映射,请参见:

-

表12-3。

-

表12-4。

12.1.6 对GIC寄存器访问效果的可观察性

PE和CPU interface逻辑必须确保:

- 对ICC_PMR_EL1的写入是自同步的。

注意 这确保在对ICC_PMR_EL1的写入在架构上执行后,不会采用优先级低于ICC_PMR_EL1中优先级值的中断。

- 当PE屏蔽中断时,即对于ICC_IAR0_EL1的读取,当PSTATE.F == 1时,以及对于ICC_IAR1_EL1的读取,当PSTATE.I == 1时,对ICC_IAR0_EL1和ICC_IAR1_EL1的读取是自同步的。

注意 这确保在对ICC_IAR0_EL1和ICC_IAR1_EL1的读取在架构上执行时,观察到激活中断对中断异常信号的影响。这意味着如果立即跟随读取的指令取消屏蔽中断,不会发生虚假的中断异常。

-

将当前异常级别从EL3更改为较低异常级别的指令,例如ERET指令,必须与中断作为FIQ和IRQ分配的任何相应更改同步,以便在指令的架构执行后不采用虚假的FIQ,请参阅_中断分配给IRQ和FIQ信号_。

-

DSB指令的架构执行保证

-

写入ICC_PMR_EL1或GICC_PMR的最后值被关联的Redistributor观察到。PMR值仅在ICC_CTLR_ELx.PMHE==1时被Redistributor观察到,Redistributor的观察不影响CPU interface内中断的屏蔽。

-

写入ICC_SGI0R_EL1或ICC_SGI1R_EL1的最后值被关联的Redistributor观察到。

-

写入ICC_ASGI1R_EL1的最后值被关联的Redistributor观察到。

-

写入ICC_IGRPEN0_EL1、ICC_IGRPEN1_EL1、ICC_IGRPEN1_EL3或GICC_CTLR.{EnableGrp0, EnableGrp1}的最后值被关联的Redistributor观察到。

-

写入ICH_VMCR_EL2.{VENG0, VENG1}或GICV_CTLR.{EnableGrp0, EnableGrp1}的最后值被关联的Redistributor观察到。

-

-

从ICC_IAR0_EL1、ICC_IAR1_EL1、GICC_IAR或GICC_AIAR读取的最后SPI INTID被Distributor和来自任何PE对Distributor的访问观察到。

-

从ICC_IAR0_EL1、ICC_IAR1_EL1、GICC_IAR或GICC_AIAR读取的最后SGI、PPI或LPI INTID被关联的Redistributor和来自PE对关联Redistributor的访问观察到。

-

从ICV_IAR1_EL1读取的最后vLPI INTID,其中该vLPI是从直接注入接收的,被关联的Redistributor观察到。

-

通过写入ICC_EOIR0_EL1、ICC_EOIR1_EL1、GICC_AEOIR、GICC_EOIR、ICC_DIR_EL1或GICC_DIR生成的SPI的最后Deactivate命令被Distributor和来自任何PE对Distributor的访问观察到。

-

通过写入ICC_EOIR0_EL1、ICC_EOIR1_EL1、GICC_AEOIR、GICC_EOIR、ICC_DIR_EL1或GICC_DIR生成的SGI或PPI的最后Deactivate命令被Redistributor和来自任何PE对Redistributor的访问观察到。

-

通过写入ICV_EOIR0_EL1、ICV_EOIR1_EL1、GICV_AEOIR、GICV_EOIR、ICV_DIR_EL1或GICV_DIR生成的物理PPI、SGI或SPI的最后Deactivate命令被Redistributor和来自任何PE对Redistributor的访问观察到。

在本节中提及DSB的所有情况下,这指的是所需访问类型为具有任何可共享属性的加载和存储的DSB。

有关DSB指令编码的更多信息,请参阅_Arm[®] Architecture Reference Manual, Armv8, for Armv8-A architecture profile_ 。

注意 ISB或其他上下文同步操作必须在DSB之前,以确保系统寄存器写入的可见性。

12.1.7 GIC系统寄存器访问

GIC系统寄存器接口由异常级别管理,使用以下AArch64系统寄存器:

-

ICC_SRE_EL3,如果实现了EL3。

-

ICC_SRE_EL2,如果实现了EL2。

-

ICC_SRE_EL1。

表12-2显示了允许的ICC_SRE_ELx.SRE设置。

表12-2 允许的ICC_SRE_ELx.SRE设置

| ICC_SRE_EL1(S) ICC_SRE_EL1(NS) ICC_SRE_EL2 ICC_SRE_EL3 | 注释 |

|---|---|

| 0 0 0 0 | Legacy,见第14章_Legacy操作和非对称配置_ |

| 0 0 0 1 | 仅在EL3使用AArch64时支持 |

| 0 0 1 1 | 仅在EL3使用AArch64且启用虚拟中断时支持 |

| 0 1 1 1 | 仅在EL3使用AArch64时支持 |

| 1 0 1 1 | 仅在HCR_EL2.FMO==1 &&HCR_EL2.IMO==1&& HCR_EL2.AMO==1时支持 注意 当HCR_EL2.FMO==1&& HCR_EL2.IMO==1时,实现允许但不要求支持此设置。 |

| 1 1 1 1 | 完全支持的系统寄存器访问 |

注意 表12-2中的信息适用于同时支持EL2和EL3的实现。

表12-2中未列出的ICC_SRE_ELx.SRE设置的所有组合导致UNPREDICTABLE行为。

除ICC_SRE_ELx.SRE == 1以外的所有设置都已弃用。

注意

-

当HCR_EL2配置为在EL1启用虚拟化时,对ICC_SRE_EL1.SRE或ICC_SRE.SRE的Non-secure访问是否可编程以支持legacy VM是IMPLEMENTATION DEFINED的。

-

Arm期望当ICC_SRE_EL3.SRE == 1且ICC_SRE_EL1(S).SRE == 0时,ICC_CTLR_EL3.RM == 1。

对ICC_SRE_ELx的以下更改导致UNPREDICTABLE行为:

-

将ICC_SRE_EL3.SRE的值从1更改为0。

-

将ICC_SRE_EL2.SRE的值从1更改为0。

-

将ICC_SRE_EL1(S).SRE的值从1更改为0。

注意 ICC_SRE_EL1(NS)可以从1更改为0,以允许不同的VM具有不同的ICC_SRE_EL1值。

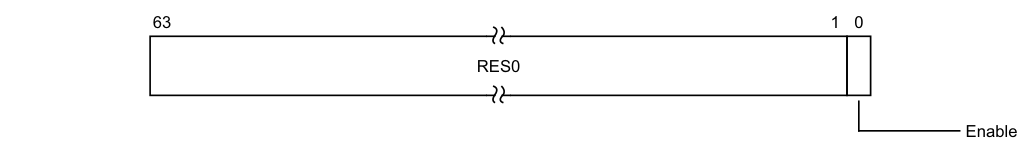

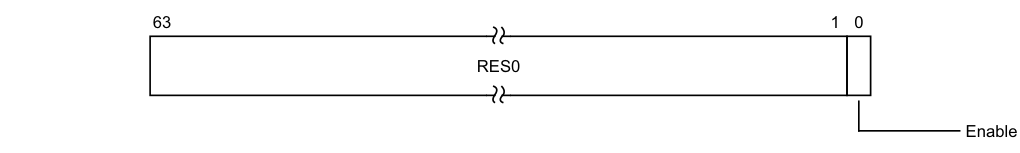

本节中列出的每个ICC_SRE_ELx寄存器提供:

-

用于在该异常级别启用ICC_*系统寄存器接口的SRE位。对于EL2和EL3,SRE位还启用对所有ICH_*寄存器的访问。

-

DIB和DFB位以支持异常级别层次结构的中断旁路。有关旁路的更多信息,请参阅_中断旁路支持_。

此外:

-

ICC_SRE_EL3.Enable控制EL1对ICC_SRE_EL1的访问,以及EL2对ICC_SRE_EL1和ICC_SRE_EL2的访问。

-

如果EL3不存在或ICC_SRE_EL3.Enable == 1,ICC_SRE_EL2.Enable控制Non-secure EL1对ICC_SRE_EL1的访问。

注意 与最高实现异常级别关联的ICC_SRE_ELx寄存器始终可访问,以允许在该异常级别执行的软件配置不同异常级别的系统寄存器。

系统寄存器接口可用于AArch32状态和AArch64状态的执行。

对于AArch32状态,对在系统寄存器接口中可见的GIC寄存器的访问使用以下指令:

-

MRC指令用于32位读访问。

-

MCR指令用于32位写访问。

-

MCRR指令用于对ICC_SGI0R、ICC_SGI1R和ICC_ASGI1R的64位写访问。

有关MRC、MCR和MCRR指令形式的信息,请参阅_Arm[®] Architecture Reference Manual, Armv8, for Armv8-A architecture profile_ 。

系统寄存器支持32位或64位访问。请参阅各个寄存器描述以了解关联的访问大小。

系统寄存器接口的访问类型定义是:

RW 读写。RO 只读。写入导致UNDEFINED异常。WO 只写。读取导致UNDEFINED异常。

注意 有关UNDEFINED异常的更多信息,请参阅_Arm[®] Architecture Reference Manual, Armv8, for Armv8-A architecture profile_ 。 表12-3显示了GIC CPU interface的系统寄存器访问的AArch64和AArch32寄存器映射。

表12-3 GIC CPU interface寄存器的系统寄存器访问

| 访问的系统寄存器名称 | 访问的系统寄存器名称 |

|---|---|

| AArch64 | AArch32 |

| ICC_IAR0_EL1a | ICC_IAR0 |

| ICC_IAR1_EL1a | ICC_IAR1 |

| ICC_EOIR0_EL1a | ICC_EOIR0 |

| ICC_EOIR1_EL1a | ICC_EOIR1 |

| ICC_HPPIR0_EL1a | ICC_HPPIR0 |

| ICC_HPPIR1_EL1a | ICC_HPPIR1 |

| ICC_BPR0_EL1a | ICC_BPR0 |

| ICC_BPR1_EL1a | ICC_BPR1 |

| ICC_DIR_EL1a | ICC_DIR |

| ICC_PMR_EL1 | ICC_PMR |

| ICC_RPR_EL1 | ICC_RPR |

| ICC_AP0R | ICC_AP0R |

| ICC_AP1R | ICC_AP1R |

| ICC_CTLR_EL1 | ICC_CTLR |

| ICC_CTLR_EL3 | ICC_MCTLR |

| ICC_IGRPEN0_EL1 | ICC_IGRPEN0 |

| ICC_IGRPEN1_EL1 | ICC_IGRPEN1 |

| ICC_IGRPEN1_EL3 | ICC_MGRPEN1 |

| ICC_SGI1R_EL1 | ICC_SGI1R |

| ICC_ASGI1R_EL1 | ICC_ASGI1R |

| ICC_SGI0R_EL1 | ICC_SGI0R |

| ICC_SRE_EL1 | ICC_SRE |

| ICC_SRE_EL2 | ICC_HSRE |

| ICC_SRE_EL3 | ICC_MSRE |

a. 除了ICC_SRE_EL*.SRE、ICC_SRE.SRE、ICC_HSRE.SRE和ICC_MSRE.SRE外,SCR_EL3和HCR_EL2控制对这些寄存器的可访问性。

当ICC_SRE_EL2.SRE == 1时,GIC virtual interface control寄存器可访问。 表12-4显示了GIC virtual interface control寄存器的AArch64和AArch32系统寄存器映射。

表12-4 GIC virtual interface control寄存器的系统寄存器映射

| 系统寄存器名称 | 访问 |

|---|---|

| AArch64 | AArch32 |

| ICH_HCR_EL2 | ICH_HCR |

| ICH_VTR_EL2 | ICH_VTR |

| ICH_MISR_EL2 | ICH_MISR |

| ICH_EISR_EL2 | ICH_EISR |

| ICH_ELRSR_EL2 | ICH_ELRSR |

| ICH_AP0R | ICH_AP0R |

| ICH_AP1R | ICH_AP1R |

| ICH_LR | ICH_LRC |

| ICH_LR | ICH_LR |

| ICH_VMCR_EL2 | ICH_VMCR |

| a. n = 0-3 | |

| b. n = 0-15。 |

AArch64系统寄存器访问指令编码

表12-5显示了访问物理和虚拟CPU interface的A64 MSR和MRS指令的格式。

表12-5 MSR和MRS到物理和虚拟CPU interface寄存器的映射,AArch64状态

| 系统寄存器 | 访问 | opc0 | opc1 | CRn | CRm | opc2 |

|---|---|---|---|---|---|---|

| ICC_AP0R | RW | 3 | 0 | c12 | c8 | 4-7 |

| ICC_AP1R | RW | 3 | 0 | c12 | c9 | 0-3 |

| ICC_ASGI1R_EL1 | WO | 3 | 0 | c12 | c11 | 6 |

| ICC_BPR0_EL1 | RW | 3 | 0 | c12 | c8 | 3 |

| ICC_BPR1_EL1b | RW | 3 | 0 | c12 | c12 | 3 |

| ICC_CTLR_EL1b | RW | 3 | 0 | c12 | c12 | 4 |

| ICC_CTLR_EL3 | RW | 3 | 6 | c12 | c12 | 4 |

| ICC_DIR_EL1 | WO | 3 | 0 | c12 | c11 | 1 |

| ICC_EOIR0_EL1 | WO | 3 | 0 | c12 | c8 | 1 |

| ICC_EOIR1_EL1 | WO | 3 | 0 | c12 | c12 | 1 |

| ICC_HPPIR0_EL1 | RO | 3 | 0 | c12 | c8 | 2 |

| ICC_HPPIR1_EL1 | RO | 3 | 0 | c12 | c12 | 2 |

| 表12-5 MSR和MRS到物理和虚拟CPU interface寄存器的映射,AArch64状态(续) |

| 系统寄存器 | 访问 | opc0 | opc1 | CRn | CRm | opc2 |

|---|---|---|---|---|---|---|

| ICC_IAR0_EL1 | RO | 3 | 0 | c12 | c8 | 0 |

| ICC_IAR1_EL1 | RO | 3 | 0 | c12 | c12 | 0 |

| ICC_IGRPEN0_EL1 | RW | 3 | 0 | c12 | c12 | 6 |

| ICC_IGRPEN1_EL1b | RW | 3 | 0 | c12 | c12 | 7 |

| ICC_IGRPEN1_EL3 | RW | 3 | 6 | c12 | c12 | 7 |

| ICC_PMR_EL1 | RW | 3 | 0 | c4 | c6 | 0 |

| ICC_RPR_EL1 | RO | 3 | 0 | c12 | c11 | 3 |

| ICC_SGI0R_EL1 | WO | 3 | 0 | c12 | c11 | 7 |

| ICC_SGI1R_EL1 | WO | 3 | 0 | c12 | c11 | 5 |

| ICC_SRE_EL1b | RW | 3 | 0 | c12 | c12 | 5 |

| ICC_SRE_EL2 | RW | 3 | 4 | c12 | c9 | 5 |

| ICC_SRE_EL3 a. n = 0-3. | RW | 3 | 6 | c12 | c12 | 5 |

| b. 此寄存器有Secure副本和Non-secure副本。 |

表12-6显示了访问virtual interface control寄存器的A64 MSR和MRS指令的格式。

表12-6 MSR和MRS到virtual interface control寄存器的映射,AArch64状态

| 系统寄存器 | 访问 | opc0 | opc1 | CRn | CRm | opc2 |

|---|---|---|---|---|---|---|

| ICH_AP0R | RW | 3 | 4 | c12 | c8 | 0-3 |

| ICH_AP1R | RW | 3 | 4 | c12 | c9 | 0-3 |

| ICH_HCR_EL2 | RW | 3 | 4 | c12 | c11 | 0 |

| ICH_VTR_EL2 | RO | 3 | 4 | c12 | c11 | 1 |

| ICH_MISR_EL2 | RO | 3 | 4 | c12 | c11 | 2 |

| ICH_EISR_EL2 | RO | 3 | 4 | c12 | c11 | 3 |

| ICH_ELRSR_EL2 | RO | 3 | 4 | c12 | c11 | 5 |

| ICH_VMCR_EL2 | RW | 3 | 4 | c12 | c11 | 7 |

| ICH_LR | RW | 3 | 4 | c12 | c12, c13 | 0-7 |

a. n = 0-15

有关A64指令的更多信息,请参阅_Arm[®] Architecture Reference Manual, Armv8, for Armv8-A architecture profile_ 。

AArch32系统寄存器访问指令编码

表12-7显示了访问物理和虚拟CPU interface的A32和T32 MCR和MRC指令的格式。

表12-7 MCR和MRC到物理和虚拟CPU interface寄存器的映射,AArch32状态

| 系统寄存器 | 访问 | opc1 | CRn | CRm | opc2 | 注释 |

|---|---|---|---|---|---|---|

| ICC_AP0R | RW | 0 | c12 | c8 | 4-7 | - |

| ICC_AP1R | RW | 0 | c12 | c9 | 0-3 | - |

| ICC_ASGI1R | WO | 1 | - | c12 | - | 使用MCRR和MRRC指令访问 |

| ICC_BPR0 | RW | 0 | c12 | c8 | 3 | - |

| ICC_BPR1a | RW | 0 | c12 | c12 | 3 | - |

| ICC_CTLRa | RW | 0 | c12 | c12 | 4 | - |

| ICC_DIR | WO | 0 | c12 | c11 | 1 | - |

| ICC_EOIR0 | WO | 0 | c12 | c8 | 1 | - |

| ICC_EOIR1 | WO | 0 | c12 | c12 | 1 | - |

| ICC_HPPIR0 | RO | 0 | c12 | c8 | 2 | - |

| ICC_HPPIR1 | RO | 0 | c12 | c12 | 2 | - |

| ICC_HSRE | RW | 4 | c12 | c9 | 5 | - |

| ICC_IAR0 | RO | 0 | c12 | c8 | 0 | - |

| ICC_IAR1 | RO | 0 | c12 | c12 | 0 | - |

| ICC_IGRPEN0 | RW | 0 | c12 | c12 | 6 | - |

| ICC_IGRPEN1a | RW | 0 | c12 | c12 | 7 | - |

| ICC_MCTLR | RW | 6 | c12 | c12 | 4 | - |

| ICC_MGRPEN1 | RW | 6 | c12 | c12 | 7 | - |

| ICC_MSRE | RW | 6 | c12 | c12 | 5 | - |

| ICC_PMR | RW | 0 | c4 | c6 | 0 | - |

| ICC_RPR | RO | 0 | c12 | c11 | 3 | - |

| ICC_SGI0R | WO | 2 | - | c12 | - | 使用MCRR和MRRC指令访问 |

| ICC_SGI1R | WO | 0 | - | c12 | - | 使用MCRR和MRRC指令访问 |

| ICC_SREa | RW | 0 | c12 | c12 | 5 | - |

a. 此寄存器有Secure副本和Non-secure副本。 表12-8显示了访问virtual interface control寄存器的A32和T32 MCR和MRC指令的格式。

表12-8 MCR和MRC到virtual interface control寄存器的映射,AArch32状态

| 系统寄存器 | 访问 | opc1 | CRn | CRm | opc2 |

|---|---|---|---|---|---|

| ICH_AP0R | RW | 4 | c12 | c8 | 0-3 |

| ICH_AP1R | RW | 4 | c12 | c9 | 0-3 |

| ICH_HCR | RW | 4 | c12 | c11 | 0 |

| ICH_VTR | RO | 4 | c12 | c11 | 1 |

| ICH_MISR | RO | 4 | c12 | c11 | 2 |

| ICH_EISR | RO | 4 | c12 | c11 | 3 |

| ICH_ELRSR | RO | 4 | c12 | c11 | 5 |

| ICH_VMCR | RW | 4 | c12 | c11 | 7 |

| ICH_LR | RW | 4 | c12 | c12, c13 | 0-7 |

| ICH_LRC | RW | 4 | c12 | c14, c15 | 0-7 |

a. n = 0-15。

有关T32和A32指令的更多信息,请参阅_Arm[®] Architecture Reference Manual, Armv8, for Armv8-A architecture profile_ 。

具有固定系统寄存器启用的实现

不需要向后兼容GICv2的GICv3实现可能具有RAO/WI的一些系统寄存器启用位。GICv3支持以下选项:

-

ICC_SRE_EL3.SRE可能是RAO/WI。这意味着在EL3执行的软件必须始终使用系统寄存器访问GIC,但较低的异常级别可能使用内存映射寄存器访问GIC。

-

如果ICC_SRE_EL3.SRE也是RAO/WI,或者如果没有实现EL3,ICC_SRE_EL2.SRE可能是RAO/WI。这意味着在EL2执行的软件必须始终使用系统寄存器访问GIC,在Non-secure EL1执行的软件可能使用内存映射寄存器访问GIC。

-

在以下情况下,ICC_SRE_EL1.SRE的Non-secure副本可能是RAO/WI:

-

没有实现EL2和EL3。

-

仅实现EL2,且ICC_SRE_EL2.SRE是RAO/WI。

-

仅实现EL3,且ICC_SRE_EL3.SRE是RAO/WI。

-

-

实现了EL2和EL3,且ICC_SRE_EL2.SRE和ICC_SRE_EL3.SRE都是RAO/WI。

这意味着在Non-secure EL1执行的软件必须始终使用系统寄存器访问GIC。

-

在以下情况下,ICC_SRE_EL1.SRE的Secure副本可能是RAO/WI:

-

没有实现EL3。

-

实现了EL3,没有实现EL2,且ICC_SRE_EL3.SRE和ICC_SRE_EL1的Non-secure副本是RAO/WI。

-

实现了EL2和EL3,且ICC_SRE_EL2.SRE和ICC_SRE_EL3.SRE都是RAO/WI。

ICC_SRE_EL3.SRE和ICC_SRE_EL2.SRE也是RAO/WI。这意味着在Secure EL1执行的软件必须使用系统寄存器访问GIC。

12.1.8 Common寄存器的访问

当为EL1的中断启用系统寄存器访问时,Group 0和Group 1中断被单独虚拟化。

这意味着在EL1操作的VM可能同时控制物理中断和虚拟中断。例如,VM可能被配置为处理:

-

通过将SCR_EL3.NS和HCR_EL2.FMO设置为1来处理虚拟Group 0中断。

-

通过将SCR_EL3.NS设置为1,并将SCR_EL3.IRQ和HCR_EL2.IMO清零为0来处理物理Group 1中断。

对于大多数操作,这种单独的虚拟化通过使用不同的寄存器来处理Group 0和Group 1中断来实现。然而,一些寄存器对Group 0和Group 1中断都是通用的。这些Common寄存器是:

-

ICC_SGI0R_EL1、ICC_SGI1R_EL1、ICC_ASGI1R_EL1。

-

ICC_CTLR_EL1。

-

ICC_DIR_EL1。

-

ICC_PMR_EL1。

-

ICC_RPR_EL1。

控制对Common寄存器的访问是物理访问、虚拟访问还是生成Trap异常的规则如下:

-

当ICH_HCR_EL2.TC == 1时,EL1的Non-secure访问生成被EL2接管的Trap异常。

-

当ICH_HCR_EL2.TDIR == 1时,EL1对ICC_DIR_EL1的Non-secure写入生成被EL2接管的Trap异常。

-

当HCR_EL2.FMO == 1 || HCR_EL2.IMO == 1时,EL1的Non-secure访问是虚拟访问:

- 对EL1可访问的所有ICC_寄存器的访问,除了ICC_SRE_EL1,改为访问等效的ICV_*寄存器。

-

对ICC_SGI0R_EL1、ICC_SGI1R_EL1和ICC_ASGI1R_EL1的虚拟访问总是生成被EL2接管的Trap异常。

否则,Common寄存器可以访问的最低异常级别是由以下任一指定的最低异常级别:

-

由SCR_EL3.FIQ、SCR_EL3.NS和HCR_EL2.FMO指定。

-

由SCR_EL3.IRQ、SCR_EL3.NS和HCR_EL2.IMO指定。

注意

Arm期望软件配置GIC使得:

-

当Group 0和Group 1配置不对称,因此访问不同状态时,ICH_HCR_EL2.TC == 1,例如一个组访问虚拟化状态,另一个组访问物理状态。

-

当配置是对称的,且对ICC_DIR_EL1的访问对Group 0和Group 1都访问物理状态或虚拟化状态时,ICH_HCR_EL2.TC == 0。

12.1.9 ICC_SRE_ELx寄存器的陷阱和启用

ICC_SRE_ELx.SRE的读/写行为控制如下:

-

ICC_SRE_EL1(NS)由ICC_SRE_EL2.{SRE, Enable}和ICC_SRE_EL3.{SRE, Enable}控制: — 如果ICC_SRE_EL2.SRE == 0或ICC_SRE_EL3.SRE == 0,则ICC_SRE_EL1.SRE(NS)是RAZ/WI。 — 如果ICC_SRE_EL2.Enable == 0,则对ICC_SRE_EL1(NS)的访问被陷阱到EL2。 — 如果ICC_SRE_EL3.Enable == 0,则对ICC_SRE_EL1(NS)的访问被陷阱到EL3。

-

ICC_SRE_EL1(S)由ICC_SRE_EL3.{SRE, Enable}控制:

-

如果ICC_SRE_EL3.SRE == 0,则ICC_SRE_EL1(S)是RAZ/WI。

-

如果ICC_SRE_EL3.Enable == 0,则对ICC_SRE_EL1(S)的访问被陷阱到EL3。

-

-

ICC_SRE_EL2由ICC_SRE_EL3.{SRE, Enable}控制: — 如果ICC_SRE_EL3.SRE == 0,则ICC_SRE_EL2.SRE是RAZ/WI。

-

如果ICC_SRE_EL2.SRE == 0,则除了读取/写入寄存器外,ICC_SRE_EL2.Enable在所有目的下都被视为1。

-

如果ICC_SRE_EL3.Enable == 0,则对ICC_SRE_EL2的访问陷阱到EL3。

-

-

如果ICC_SRE_EL3.SRE == 0,则除了读取或写入寄存器外,ICC_SRE_EL3.Enable在所有目的下都被视为1。

-

在包含EL3的实现中,如果ICC_SRE_EL1(S).SRE == 1且ICC_SRE_EL3.SRE == 1,则ICC_SRE_EL2.SRE == 0导致UNPREDICTABLE行为。

在以下表格中:

-

x 表示该位可以是0或1。

-

表示此访问不适用。

-

[0] RAZ/WI。读取返回0,写入被忽略。此位被视为0。

-

{1} 除了读取/写入寄存器外,此位在所有目的下都被视为1。

-

(1) 此位必须设置为1,否则行为是UNPREDICTABLE。

-

NS 表示SCR_EL3.NS的值。RW 表示允许读/写访问。

-

T(EL2) 生成被EL2接管的Trap异常。

-

T(EL3) 生成被EL3接管的Trap异常。当EL3使用AArch32时,这被替换为被当前异常级别接管的Undefined异常。

UND 生成UNDEFINED异常或到当前异常级别的陷阱。

表12-9显示了ICC_SRE_EL3可以访问的条件。

表12-9 ICC_SRE_EL3访问

| ICC_SRE_EL3 | ICC_SRE_EL3 | ICC_SRE_EL2 | ICC_SRE_EL2 | ICC_SRE_EL1 | ICC_SRE_EL1 | EL1 | EL2 | EL3 | |

|---|---|---|---|---|---|---|---|---|---|

| SRE | Enable | SRE | Enable | SRE NS=0 | SRE NS=1 | NS = 0 | NS = 1 | NS = 1 | |

| x | x | x | x | x | x | UND | UND | UND | RW |

表12-10显示了ICC_SRE_EL2可以访问的条件。

表12-10 ICC_SRE_EL2访问

| ICC_SRE_EL3 | ICC_SRE_EL3 | ICC_SRE_EL2 | ICC_SRE_EL2 | ICC_SRE_EL1 | ICC_SRE_EL1 | EL1 | EL2 | EL3 | ||

|---|---|---|---|---|---|---|---|---|---|---|

| SRE | Enable | SRE | Enable | SRE NS=0 | SRE NS=1 | NS=0 | NS=1 | NS = 1 | NS=0 | NS=1 |

| 0 | {1} | [0] | {1} | [0] | [0] | UND | UND | RW | UND | RW |

| 1 | 0 | x | x | 0 | x | UND | UND | T(EL3) | UND | RW |

| 1 | 0 | (1) | x | 1 | x | UND | UND | T(EL3) | UND | RW |

| 1 | 1 | x | x | 0 | x | UND | UND | RW | UND | RW |

| 1 | 1 | (1) | x | 1 | x | UND | UND | RW | UND | RW |

| 表12-11显示了当实现EL3时ICC_SRE_EL1(S)可以访问的条件。 |

表12-11 ICC_SRE_EL1(S)访问

| ICC_SRE_EL3 | ICC_SRE_EL3 | ICC_SRE_EL2 | ICC_SRE_EL2 | ICC_SRE_EL1 | ICC_SRE_EL1 | EL1 | EL2 | EL3 | ||

|---|---|---|---|---|---|---|---|---|---|---|

| SRE | Enable | SRE | Enable | SRE NS=0 | SRE NS=1 | NS=0 | NS=1 | NS = 1 | NS=0 | NS=1 |

| 0 | {1} | [0] | {1} | [0] | [0] | RW | N/A | N/A | RW | N/A |

| 1 | 0 | x | x | x | x | T(EL3) | N/A | N/A | RW | N/A |

| 1 | 1 | x | x | x | x | RW | N/A | N/A | RW | N/A |

表12-12显示了当实现EL3时ICC_SRE_EL1(NS)可以访问的条件。

表12-12 ICC_SRE_EL1(NS)访问

| ICC_SRE_EL3 | ICC_SRE_EL3 | ICC_SRE_EL2 | ICC_SRE_EL2 | ICC_SRE_EL1 | ICC_SRE_EL1 | EL1 | EL2 | EL3 | ||

|---|---|---|---|---|---|---|---|---|---|---|

| SRE | Enable | SRE | Enable | SRE NS=0 | SRE NS=1 | NS=0 | NS=1 | NS = 1 | NS=0 | NS=1 |

| 0 | {1} | [0] | {1} | [0] | [0] | N/A | RW | RW | N/A | RW |

| 1 | 0 | 0 | {1} | 0 | [0] | N/A | T(EL3) | T(EL3) | N/A | RW |

| 1 | 1 | 0 | {1} | 0 | [0] | N/A | RW | RW | N/A | RW |

| 1 | 0 | (1) | 0 | 1 | x | N/A | T(EL2) | T(EL3) | N/A | RW |

| 1 | 1 | (1) | 0 | 1 | x | N/A | T(EL2) | RW | N/A | RW |

| 1 | 0 | (1) | 1 | 1 | x | N/A | T(EL3) | T(EL3) | N/A | RW |

| 1 | 1 | (1) | 1 | 1 | x | N/A | RW | RW | N/A | RW |

| 1 | 0 | 1 | 0 | 0 | x | N/A | T(EL2) | T(EL3) | N/A | RW |

| 1 | 1 | 1 | 0 | 0 | x | N/A | T(EL2) | RW | N/A | RW |

| 1 | 0 | 1 | 1 | 0 | x | N/A | T(EL3) | T(EL3) | N/A | RW |

| 1 | 1 | 1 | 1 | 0 | x | N/A | RW | RW | N/A | RW |

表12-13显示了当没有实现EL3时ICC_SRE_EL1的单个副本可以访问的条件。

表12-13 ICC_SRE_EL1访问

| ICC_SRE_EL2 | ICC_SRE_EL2 | ICC_SRE_EL1 | EL1 | EL2 |

|---|---|---|---|---|

| SRE | Enable | |||

| 0 | {1} | [0] | RW | RW |

| 0 | 1 | [0] | RW | RW |

| 1 | 0 | x | T(EL2) | RW |

| 1 | 1 | x | RW | RW |

| 这些表中未描述的访问是不可能的。 |

12.1.10 使用控制寄存器进行SGI转发

表12-14显示了决定访问哪个SGI寄存器以及当启用亲和路由时是否将SGI转发到指定目标CPU interface的条件。

表12-14 将SGI转发到目标PE |—|—|—| | 访问 | 访问的SGI寄存器 AArch64 AArch32 | 目标PE上指定SGI的配置 信号SGI? | | Secure EL1 Secure EL2 EL3 | ICC_SGI1R_EL1 ICC_SGI1R ICC_ASGI1R_EL1 ICC_ASGI1R ICC_SGI0R_EL1 ICC_SGI0R | Secure Group 0 是,前提是GICD_CTLR.DS == 1 Secure Group 1 是 Non-secure Group 1 否 Secure Group 0 否 Secure Group 1 否 Non-secure Group 1 是 Secure Group 0 是 Secure Group 1 否 Non-secure Group 1 否 | 表12-14 将SGI转发到目标PE(续)

| 访问 | 访问的SGI寄存器 AArch64 AArch32 | 目标PE上指定SGI的配置 信号SGI? |

|---|---|---|

| Non-secure EL1 Non-secure EL2 | ICC_SGI1R_EL1 ICC_SGI1R ICC_ASGI1R_EL1 ICC_ASGI1R ICC_SGI0R_EL1 ICC_SGI0R | Secure Group 0 是,前提是满足以下任一条件: • 每个目标PE的GICR_NSACR中的相应字段允许此操作。 • GICD_CTLR.DS == 1。 Secure Group 1 是,如果每个目标PE的GICR_NSACR中的相应字段允许。 Non-secure Group 1 是 Secure Group 0 是,前提是满足以下任一条件: • 每个目标PE的GICR_NSACR中的相应字段允许此操作。 • GICD_CTLR.DS == 1。 Secure Group 1 如果GICR_NSACR中的相应字段允许。 Non-secure Group 1 否 Secure Group 0 是,前提是满足以下任一条件: • 每个目标PE的GICR_NSACR中的相应字段允许此操作。 • GICD_CTLR.DS == 1。 Secure Group 1 否 Non-secure Group 1 否 |

注意

-

当Secure EL1未启用系统寄存器访问,或当GICD_CTLR.DS == 1时,Distributor将Secure Group 1中断视为Group 0中断。当表12-14指示生成Secure Group 1中断时,Distributor必须向CPU interface发送Secure Group 0中断。

-

为其他安全状态生成SGI仅在两种安全状态都启用亲和路由时才支持。

-

对于具有单一安全状态的PE,或当GICD_CTLR.DS==1时,请参阅表4-6以了解SCR_EL3.NS的有效值信息。

12.1.11 GIC安全状态

当GIC支持两种安全状态时,PE对GIC寄存器访问的行为取决于访问是Secure还是Non-secure。除非本文档明确另有说明,当访问GIC寄存器时:

-

对保存Secure中断状态信息的寄存器字段的Non-secure读取返回零。

-

GIC忽略对保存Secure中断状态信息的寄存器字段的任何Non-secure写入。

Arm架构定义了以下寄存器类型:

Banked 设备实现寄存器的Secure和Non-secure副本。有关更多信息,请参阅_寄存器银行_。Secure 寄存器仅可从Secure访问。Secure寄存器的地址对任何Non-secure访问都是RAZ/WI。

Common 寄存器可从Secure和Non-secure访问。寄存器中某些或所有字段的访问权限可能取决于访问是Secure还是Non-secure。

12.1.12 寄存器银行

寄存器银行是指提供寄存器的多个副本。GIC在以下情况下对寄存器进行银行:

-

如果GIC支持两种安全状态,一些寄存器被银行以提供寄存器的单独Secure和Non-secure副本。Secure和Non-secure寄存器位分配可能不同。对寄存器地址的Secure访问访问寄存器的Secure副本,Non-secure访问访问Non-secure副本。

-

如果GIC作为多处理器系统的一部分实现:

-

一些寄存器被银行以为每个连接的PE提供单独的副本。这些包括与PPI和SGI关联的寄存器,以及GICD_NSACR

(其中n=0,当实现时)。 -

GIC为每个CPU interface独立实现CPU interface寄存器,每个连接的PE访问它连接的接口的寄存器。

-

以下GIC系统寄存器按安全状态进行银行:

-

ICC_AP1R

_EL1。 -

ICC_BPR1_EL1。

-

ICC_CTLR_EL1。

-

ICC_IGRPEN1_EL1。

-

ICC_SRE_EL1。

注意 这些是唯一按安全状态进行银行的Armv8 AArch64系统寄存器。

在legacy操作支持物理中断的地方,以下GICC_*内存映射寄存器按安全状态进行银行:

-

GICC_CTLR。

-

GICC_BPR。

12.1.13 识别寄存器

寄存器偏移量0xFFD0-0xFFFC被定义为只读识别寄存器空间。对于GIC架构的Arm实现,此寄存器空间的分配以及此空间中寄存器的命名与CoreLink和CoreSight组件的Arm识别方案一致。

注意 Arm强烈建议其他实现者也使用此方案以提供一致的软件发现模型。 架构规范在Distributor寄存器映射中将偏移量0xFFD0 - 0xFFFC定义为识别寄存器空间,如表12-15所示。

表12-15 GIC识别寄存器空间,Distributor寄存器映射

| 偏移量 | 名称 | 类型 | 描述 |

|---|---|---|---|

| 0xFFD0-0xFFE4 | - | RO | IMPLEMENTATION DEFINED寄存器 |

| 0xFFE8 | GICD_PIDR2 | RO | Distributor Peripheral ID2寄存器 |

| 0xFFEC-0xFFFC | - | RO | IMPLEMENTATION DEFINED寄存器 |

架构规范在Redistributor寄存器映射中将偏移量0xFFD0 - 0xFFFC定义为识别寄存器空间,如表12-16所示。

表12-16 GIC识别寄存器空间,Redistributor寄存器映射

| 偏移量 | 名称 | 类型 | 描述 |

|---|---|---|---|

| 0xFFD0-0xFFE4 | - | RO | IMPLEMENTATION DEFINED寄存器 |

| 0xFFE8 | GICR_PIDR2 | RO | Redistributor Peripheral ID2寄存器 |

| 0xFFEC-0xFFFC | - | RO | IMPLEMENTATION DEFINED寄存器 |

架构规范在ITS寄存器映射中将偏移量0xFFD0 - 0xFFFC定义为识别寄存器空间,如表12-17所示。

表12-17 GIC识别寄存器空间,ITS寄存器映射

| 偏移量 | 名称 | 类型 | 描述 |

|---|---|---|---|

| 0xFFD0-0xFFE4 | - | RO | IMPLEMENTATION DEFINED寄存器 |

| 0xFFE8 | GITS_PIDR2 | RO | ITS Peripheral ID2寄存器 |

| 0xFFEC-0xFFFC | - | RO | IMPLEMENTATION DEFINED寄存器 |

Arm通用ID寄存器可以在IMPLEMENTATION DEFINED寄存器空间中使用。

12.2 AArch64 系统寄存器描述

本节按寄存器名称顺序描述每个物理 AArch64 GIC 系统寄存器。ICC 前缀表示 GIC CPU 接口系统寄存器。每个 AArch64 系统寄存器描述包含对提供相同功能的 AArch32 寄存器的引用。

除非另有说明,GIC 系统寄存器的位分配与等效的 GICC_* 和 GICV_* 内存映射寄存器相同。

ICC 前缀由系统寄存器访问机制使用,根据 HCR_EL2 的设置选择物理或虚拟接口系统寄存器。等效的内存映射物理寄存器在 GIC CPU 接口寄存器描述 中描述。等效的虚拟接口内存映射寄存器在 GIC 虚拟 CPU 接口寄存器描述 中描述。

表 12-21 显示了 AArch64 系统寄存器的编码。

表 12-21 AArch64 系统寄存器编码

| 寄存器 宽度(位) ICC_PMR_EL1 32 | 访问指令编码 Op0 Op1 CRn CRm | 访问指令编码 Op0 Op1 CRn CRm | 访问指令编码 Op0 Op1 CRn CRm | 注释 Op2 0 RW |

|—|— 3 0 |— 4 |— 6 |—|

| ICC_IAR0_EL1 32 | | 12 | 8 | 0 RO |

| ICC_EOIR0_EL1 32 | | | | 1 WO |

| ICC_HPPIR0_EL1 32 | | | | 2 RO |

| ICC_BPR0_EL1 32 | | | | 3 RW |

| ICC_AP0R

表 12-21 AArch64 系统寄存器编码(续)

| ICC_CTLR_EL3 32 寄存器 宽度(位) | 访问指令编码 Op0 Op1 CRn CRm | 4 RW 注释 Op2 | |—|— 3 6 12 12 |—| | ICC_SRE_EL3 32 | | 5 RW | | ICC_IGRPEN1_EL3 32 | | 7 RW |

以下访问编码是 IMPLEMENTATION DEFINED。

| op0 | op1 | CRn | CRm | op2 |

|---|---|---|---|---|

| 11 | 000 | 1100 | 1101 | 000 |

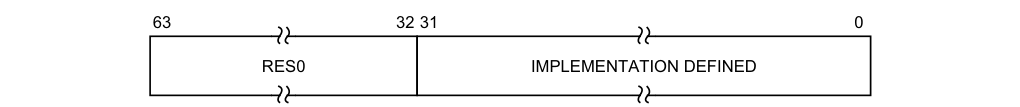

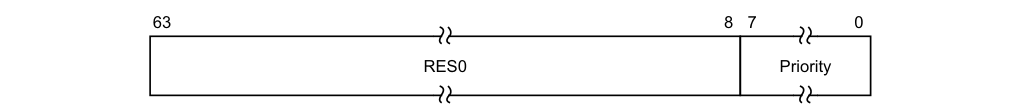

12.2.1 ICC_AP0R_EL1, 中断控制器活跃优先级 Group 0 寄存器, n = 0 - 3

ICC_AP0R

目的

提供关于 Group 0 活跃优先级的信息。

配置

AArch64 系统寄存器 ICC_AP0R

属性

ICC_AP0R

字段描述

ICC_AP0R

| | 63 | | 32 | 31 | | 0 | | |—|—|— RES0 |—|—|— IMPLEMENTATION DEFINED |—|—| |||||||||

位 [63:32]

保留,RES0。

IMPLEMENTATION DEFINED, 位 [31:0]

IMPLEMENTATION DEFINED。

在热复位时,此字段复位为 0。

这些寄存器的内容是 IMPLEMENTATION DEFINED,只有一个架构要求是值 0x00000000 与没有中断处于活跃状态一致。

访问 ICC_AP0R_EL1

用除寄存器上次读取值(或在没有 Group 0 活跃优先级时为 0x00000000)之外的任何值写入这些寄存器可能导致中断优先级系统的 UNPREDICTABLE 行为,造成:

-

应该抢占执行的中断不抢占执行。

-

不应该抢占执行的中断抢占执行。

ICC_AP0R1_EL1 只在支持 6 位或更多优先级位的实现中实现。

ICC_AP0R2_EL1 和 ICC_AP0R3_EL1 只在支持 7 位或更多优先级位的实现中实现。未实现的寄存器是 UNDEFINED。

注意 抢占位数由 ICH_VTR_EL2.PREbits 指示。

按除以下顺序外的任何顺序写入活跃优先级寄存器将导致 UNPREDICTABLE 行为:

-

ICC_AP0R

_EL1。 -

安全 ICC_AP1R

_EL1。 -

非安全 ICC_AP1R

_EL1。

访问此寄存器使用系统指令编码空间中的以下编码:

MRS , ICC_AP0R_EL1

| op0 | op1 | CRn | CRm | op2 |

|---|---|---|---|---|

| 0b11 | 0b000 | 0b1100 | 0b1000 | 0b1:n[1:0] |

if PSTATE.EL == EL0 then UNDEFINED;

elsif PSTATE.EL == EL1 then

if Halted() && HaveEL(EL3) && EDSCR.SDD == '1' &&

boolean IMPLEMENTATION_DEFINED "EL3 trap priority

when SDD == '1'" && SCR_EL3.FIQ == '1' then UNDEFINED;

elsif ICC_SRE_EL1.SRE == '0' then AArch64.SystemAccessTrap(EL1, 0x18);

elsif EL2Enabled() && ICH_HCR_EL2.TALL0 == '1' then AArch64.SystemAccessTrap(EL2, 0x18);

elsif EL2Enabled() && HCR_EL2.FMO == '1' then

return ICV_AP0R_EL1[UInt(op2<1:0>)];

elsif HaveEL(EL3) && SCR_EL3.FIQ == '1' then

if Halted() && EDSCR.SDD == '1' then UNDEFINED;

else AArch64.SystemAccessTrap(EL3, 0x18);

else return ICC_AP0R_EL1[UInt(op2<1:0>)];

elsif PSTATE.EL == EL2 then

if Halted() && HaveEL(EL3) && EDSCR.SDD == '1' &&

boolean IMPLEMENTATION_DEFINED "EL3 trap priority

when SDD == '1'" && SCR_EL3.FIQ == '1' then UNDEFINED;

elsif ICC_SRE_EL2.SRE == '0' then AArch64.SystemAccessTrap(EL2, 0x18);

elsif HaveEL(EL3) && SCR_EL3.FIQ == '1' then

if Halted() && EDSCR.SDD == '1' then UNDEFINED;

else AArch64.SystemAccessTrap(EL3, 0x18);

else return ICC_AP0R_EL1[UInt(op2<1:0>)];

elsif PSTATE.EL == EL3 then

if ICC_SRE_EL3.SRE == '0' then AArch64.SystemAccessTrap(EL3, 0x18);

else return ICC_AP0R_EL1[UInt(op2<1:0>)];

MSR ICC_AP0R_EL1,

| op0 | op1 | CRn | CRm | op2 |

|---|---|---|---|---|

| 0b11 | 0b000 | 0b1100 | 0b1000 | 0b1:n[1:0] |

if PSTATE.EL == EL0 then UNDEFINED;

elsif PSTATE.EL == EL1 then

if Halted() && HaveEL(EL3) && EDSCR.SDD == '1' &&

boolean IMPLEMENTATION_DEFINED "EL3 trap priority

when SDD == '1'" && SCR_EL3.FIQ == '1' then

UNDEFINED;

elsif ICC_SRE_EL1.SRE == '0'

then AArch64.SystemAccessTrap(EL1, 0x18);

elsif EL2Enabled() && ICH_HCR_EL2.TALL0 == '1'

then AArch64.SystemAccessTrap(EL2, 0x18);

elsif EL2Enabled() && HCR_EL2.FMO == '1'

then ICV_AP0R_EL1[UInt(op2<1:0>)] = X[t];

elsif HaveEL(EL3) && SCR_EL3.FIQ == '1' then

if Halted() && EDSCR.SDD == '1' then UNDEFINED;

else AArch64.SystemAccessTrap(EL3, 0x18);

else ICC_AP0R_EL1[UInt(op2<1:0>)] = X[t];

elsif PSTATE.EL == EL2 then

if Halted() && HaveEL(EL3) && EDSCR.SDD == '1' &&

boolean IMPLEMENTATION_DEFINED "EL3 trap priority

when SDD == '1'" && SCR_EL3.FIQ == '1' then UNDEFINED;

elsif ICC_SRE_EL2.SRE == '0' then AArch64.SystemAccessTrap(EL2, 0x18);

elsif HaveEL(EL3) && SCR_EL3.FIQ == '1' then

if Halted() && EDSCR.SDD == '1' then UNDEFINED;

else AArch64.SystemAccessTrap(EL3, 0x18);

else ICC_AP0R_EL1[UInt(op2<1:0>)] = X[t];

elsif PSTATE.EL == EL3 then

if ICC_SRE_EL3.SRE == '0' then AArch64.SystemAccessTrap(EL3, 0x18);

else ICC_AP0R_EL1[UInt(op2<1:0>)] = X[t];

12.2.2 ICC_AP1R_EL1, 中断控制器活跃优先级 Group 1 寄存器, n = 0 - 3

ICC_AP1R

目的

提供关于 Group 1 活跃优先级的信息。

配置

AArch64 系统寄存器 ICC_AP1R

AArch64 系统寄存器 ICC_AP1R

属性

ICC_AP1R

字段描述

ICC_AP1R

| | 63 | | 32 | 31 | | 0 | | |—|—|— RES0 |—|—|— IMPLEMENTATION DEFINED |—|—| |||||||||

位 [63:32]

保留,RES0。

IMPLEMENTATION DEFINED, 位 [31:0]

IMPLEMENTATION DEFINED。

在热复位时,此字段复位为 0。

这些寄存器的内容是 IMPLEMENTATION DEFINED,只有一个架构要求是值 0x00000000 与没有中断处于活跃状态一致。

访问 ICC_AP1R_EL1

用除寄存器上次读取值(或在没有 Group 1 活跃优先级时为 0x00000000)之外的任何值写入这些寄存器可能导致中断优先级系统的 UNPREDICTABLE 行为,造成:

-

应该抢占执行的中断不抢占执行。

-

不应该抢占执行的中断抢占执行。

ICC_AP1R1_EL1 只在支持 6 位或更多优先级位的实现中实现。

ICC_AP1R2_EL1 和 ICC_AP1R3_EL1 只在支持 7 位或更多优先级位的实现中实现。未实现的寄存器是 UNDEFINED。

注意 抢占位数由 ICH_VTR_EL2.PREbits 指示。

按除以下顺序外的任何顺序写入活跃优先级寄存器将导致 UNPREDICTABLE 行为:

-

ICC_AP0R

_EL1。 -

安全 ICC_AP1R

_EL1。 -

非安全 ICC_AP1R

_EL1。

访问此寄存器使用系统指令编码空间中的以下编码:

MRS , ICC_AP1R_EL1

| op0 | op1 | CRn | CRm | op2 |

|---|---|---|---|---|

| 0b11 | 0b000 | 0b1100 | 0b1001 | 0b0:n[1:0] |

if PSTATE.EL == EL0 then UNDEFINED;

elsif PSTATE.EL == EL1 then

if Halted() && HaveEL(EL3) && EDSCR.SDD == '1' &&

boolean IMPLEMENTATION_DEFINED "EL3 trap priority

when SDD == '1'" && SCR_EL3.IRQ == '1' then UNDEFINED;

elsif ICC_SRE_EL1.SRE == '0' then AArch64.SystemAccessTrap(EL1, 0x18);

elsif EL2Enabled() && ICH_HCR_EL2.TALL1 == '1' then AArch64.SystemAccessTrap(EL2, 0x18);

elsif EL2Enabled() && HCR_EL2.IMO == '1' then

return ICV_AP1R_EL1[UInt(op2<1:0>)];

elsif HaveEL(EL3) && SCR_EL3.IRQ == '1' then

if Halted() && EDSCR.SDD == '1' then UNDEFINED;

else AArch64.SystemAccessTrap(EL3, 0x18);

elsif HaveEL(EL3) then

if SCR_EL3.NS == '0' then

return ICC_AP1R_EL1_S[UInt(op2<1:0>)];

else return ICC_AP1R_EL1_NS[UInt(op2<1:0>)];

else return ICC_AP1R_EL1[UInt(op2<1:0>)];

elsif PSTATE.EL == EL2 then

if Halted() && HaveEL(EL3) && EDSCR.SDD == '1' &&

boolean IMPLEMENTATION_DEFINED "EL3 trap priority

when SDD == '1'" && SCR_EL3.IRQ == '1' then UNDEFINED;

elsif ICC_SRE_EL2.SRE == '0' then AArch64.SystemAccessTrap(EL2, 0x18);

elsif HaveEL(EL3) && SCR_EL3.IRQ == '1' then

if Halted() && EDSCR.SDD == '1' then UNDEFINED;

else AArch64.SystemAccessTrap(EL3, 0x18);

elsif HaveEL(EL3) then

if SCR_EL3.NS == '0' then

return ICC_AP1R_EL1_S[UInt(op2<1:0>)];

else return ICC_AP1R_EL1_NS[UInt(op2<1:0>)];

else return ICC_AP1R_EL1[UInt(op2<1:0>)];

elsif PSTATE.EL == EL3 then

if ICC_SRE_EL3.SRE == '0' then AArch64.SystemAccessTrap(EL3, 0x18);

else if SCR_EL3.NS == '0' then

return ICC_AP1R_EL1_S[UInt(op2<1:0>)];

else return ICC_AP1R_EL1_NS[UInt(op2<1:0>)];

MSR ICC_AP1R_EL1,

| op0 | op1 | CRn | CRm | op2 |

|---|---|---|---|---|

| 0b11 | 0b000 | 0b1100 | 0b1001 | 0b0:n[1:0] |

if PSTATE.EL == EL0 then UNDEFINED;

elsif PSTATE.EL == EL1 then

if Halted() && HaveEL(EL3) && EDSCR.SDD == '1' &&

boolean IMPLEMENTATION_DEFINED "EL3 trap priority

when SDD == '1'" && SCR_EL3.IRQ == '1' then UNDEFINED;

elsif ICC_SRE_EL1.SRE == '0' then AArch64.SystemAccessTrap(EL1, 0x18);

elsif EL2Enabled() && ICH_HCR_EL2.TALL1 == '1' then AArch64.SystemAccessTrap(EL2, 0x18);

elsif EL2Enabled() && HCR_EL2.IMO == '1' then ICV_AP1R_EL1[UInt(op2<1:0>)] = X[t];

elsif HaveEL(EL3) && SCR_EL3.IRQ == '1' then

if Halted() && EDSCR.SDD == '1' then UNDEFINED;

else AArch64.SystemAccessTrap(EL3, 0x18);

elsif HaveEL(EL3) then

if SCR_EL3.NS == '0' then ICC_AP1R_EL1_S[UInt(op2<1:0>)] = X[t];

else ICC_AP1R_EL1_NS[UInt(op2<1:0>)] = X[t];

else ICC_AP1R_EL1[UInt(op2<1:0>)] = X[t];

elsif PSTATE.EL == EL2 then

if Halted() && HaveEL(EL3) && EDSCR.SDD == '1' &&

boolean IMPLEMENTATION_DEFINED "EL3 trap priority

when SDD == '1'" && SCR_EL3.IRQ == '1' then UNDEFINED;

elsif ICC_SRE_EL2.SRE == '0' then AArch64.SystemAccessTrap(EL2, 0x18);

elsif HaveEL(EL3) && SCR_EL3.IRQ == '1' then

if Halted() && EDSCR.SDD == '1' then UNDEFINED;

else AArch64.SystemAccessTrap(EL3, 0x18);

elsif HaveEL(EL3) then

if SCR_EL3.NS == '0' then ICC_AP1R_EL1_S[UInt(op2<1:0>)] = X[t];

else ICC_AP1R_EL1_NS[UInt(op2<1:0>)] = X[t];

else ICC_AP1R_EL1[UInt(op2<1:0>)] = X[t];

elsif PSTATE.EL == EL3 then

if ICC_SRE_EL3.SRE == '0' then AArch64.SystemAccessTrap(EL3, 0x18);

else if SCR_EL3.NS == '0' then ICC_AP1R_EL1_S[UInt(op2<1:0>)] = X[t];

else ICC_AP1R_EL1_NS[UInt(op2<1:0>)] = X[t];

12.2.3 ICC_ASGI1R_EL1, 中断控制器别名软件生成中断 Group 1 寄存器

ICC_ASGI1R_EL1 特性如下:

目的

为非当前安全状态的安全状态生成 Group 1 SGI。

配置

AArch64 系统寄存器 ICC_ASGI1R_EL1 执行与 AArch32 系统寄存器 ICC_ASGI1R 相同的功能。在某些条件下,写入 ICC_ASGI1R_EL1 可以生成 Group 0 中断,请参见表 12-14。

属性

ICC_ASGI1R_EL1 是 64 位寄存器。

字段描述

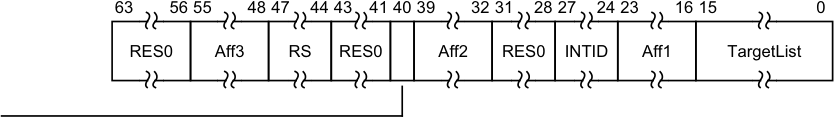

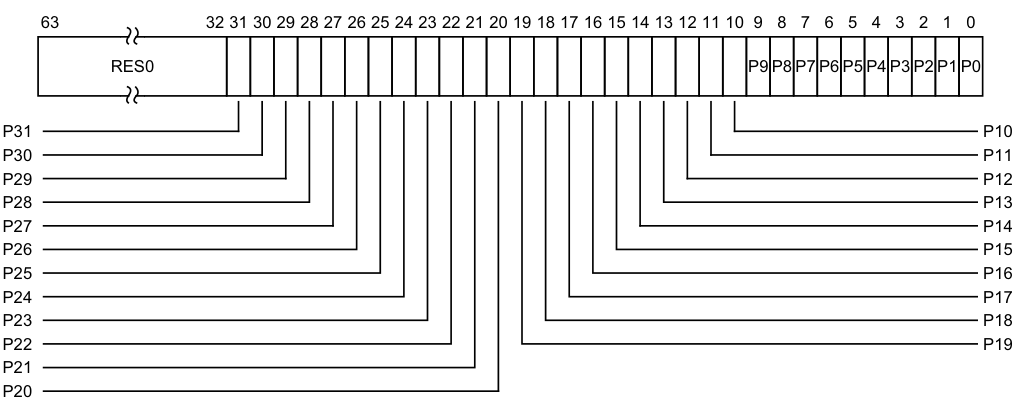

ICC_ASGI1R_EL1 位分配:

IRM

63 56 55 48 47 44 43 41 40 39 32 31 28 27 24 23 16 15 0

RES0 Aff3 RS RES0 Aff2 RES0 INTID Aff1 TargetList

位 [63:56]

保留,RES0。

Aff3, 位 [55:48]

要生成 SGI 中断的簇的亲和路径的亲和性 3 值。如果 IRM 位是 1,此字段是 RES0。

RS, 位 [47:44]

RangeSelector 控制 TargetList 字段表示的 16 个值的组。TargetList[n] 表示 aff0 值 ((RS * 16) + n)。当 ICC_CTLR_EL1.RSS==0 时,RS 是 RES0。当 ICC_CTLR_EL1.RSS==1 且 GICD_TYPER.RSS==0 时,使用 RS != 0 写入此寄存器是 CONSTRAINED UNPREDICTABLE 选择:• 写入被忽略。• RS 字段被视为 0。

位 [43:41]

保留,RES0。

IRM, 位 [40]

中断路由模式。确定生成的中断如何分发到 PE。可能的值是:0b0 中断路由到 Aff3.Aff2.Aff1.<目标列表> 指定的 PE。0b1 中断路由到系统中的所有 PE,不包括“自己“。

Aff2, 位 [39:32]

要生成 SGI 中断的簇的亲和路径的亲和性 2 值。如果 IRM 位是 1,此字段是 RES0。

位 [31:28]

保留,RES0。

INTID, 位 [27:24]

SGI 的 INTID。

Aff1, 位 [23:16]

要生成 SGI 中断的簇的亲和路径的亲和性 1 值。

如果 IRM 位是 1,此字段是 RES0。

TargetList, 位 [15:0]

目标列表。要生成 SGI 中断的 PE 集合。每个位对应簇中亲和性 0 值等于位号的 PE。

如果位是 1 且该位不对应有效的目标 PE,则分发器必须忽略该位。在这种情况下,分发器是否可以发出系统错误信号是 IMPLEMENTATION DEFINED。

注意 这限制了系统只能向亲和性 0 号小于 16 的 PE 发送定向 SGI。如果 SRE 仅对安全 EL3 设置,在 EL3 执行的软件可能使用系统寄存器接口生成 SGI。因此,分发器必须始终能够接收和确认从 CPU 接口接收到的生成 SGI 数据包,无论安全状态的 ARE 设置如何。然而,分发器可能丢弃这些数据包。

如果 IRM 位是 1,此字段是 RES0。

访问 ICC_ASGI1R_EL1

此寄存器允许在安全状态下执行的软件生成非安全 Group 1 SGI。如果目标 PE 对应的重分发器中的 GICR_NSACR 设置允许,它还允许在非安全状态下执行的软件生成安全 Group 1 SGI。

当 GICD_CTLR.DS==0 时,如果目标 PE 关联的 GICR_NSACR 寄存器不允许,非安全写入不会为目标 PE 生成中断。有关更多信息,请参见 SGI 转发的控制寄存器使用。

注意 EL3 的访问被视为安全,无论 SCR_EL3.NS 的值如何。

访问此寄存器使用系统指令编码空间中的以下编码:

MSR ICC_ASGI1R_EL1,

| op0 | op1 | CRn | CRm | op2 |

|---|---|---|---|---|

| 0b11 | 0b000 | 0b1100 | 0b1011 | 0b110 |

if PSTATE.EL == EL0 then UNDEFINED;

elsif PSTATE.EL == EL1 then

if Halted() && HaveEL(EL3) && EDSCR.SDD == '1' &&

boolean IMPLEMENTATION_DEFINED "EL3 trap priority

when SDD == '1'" && SCR_EL3.<IRQ,FIQ> == '11' then

UNDEFINED;

elsif ICC_SRE_EL1.SRE == '0'

then AArch64.SystemAccessTrap(EL1, 0x18);

elsif EL2Enabled() && ICH_HCR_EL2.TC == '1'

then AArch64.SystemAccessTrap(EL2, 0x18);

elsif EL2Enabled() && HCR_EL2.FMO == '1'

then AArch64.SystemAccessTrap(EL2, 0x18);

elsif EL2Enabled() && HCR_EL2.IMO == '1'

then AArch64.SystemAccessTrap(EL2, 0x18);

elsif HaveEL(EL3) && SCR_EL3.<IRQ,FIQ> == '11'

then if Halted() && EDSCR.SDD == '1'

then UNDEFINED;

else AArch64.SystemAccessTrap(EL3, 0x18);

else ICC_ASGI1R_EL1 = X[t];

elsif PSTATE.EL == EL2

then if Halted() && HaveEL(EL3) && EDSCR.SDD == '1' && boolean IMPLEMENTATION_DEFINED "EL3 trap priority when SDD == '1'" && SCR_EL3.<IRQ,FIQ> == '11'

then UNDEFINED;

elsif ICC_SRE_EL2.SRE == '0'

then AArch64.SystemAccessTrap(EL2, 0x18);

elsif HaveEL(EL3) && SCR_EL3.<IRQ,FIQ> == '11'

then if Halted() && EDSCR.SDD == '1'

then UNDEFINED;

else AArch64.SystemAccessTrap(EL3, 0x18);

else ICC_ASGI1R_EL1 = X[t];

elsif PSTATE.EL == EL3

then if ICC_SRE_EL3.SRE == '0'

then AArch64.SystemAccessTrap(EL3, 0x18);

else ICC_ASGI1R_EL1 = X[t];

续 - 由于文件太长,我将分段完成翻译,确保遵循所有格式要求

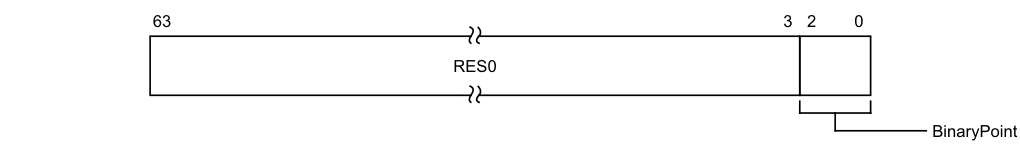

12.2.4 ICC_BPR0_EL1, 中断控制器二进制分割点寄存器 0

ICC_BPR0_EL1 特性如下:

目的

定义优先级值字段分割为两部分的点,即组优先级字段和子优先级字段。组优先级字段决定 Group 0 中断抢占。

配置

AArch64 系统寄存器 ICC_BPR0_EL1 位 [31:0] 在架构上映射到 AArch32 系统寄存器 ICC_BPR0[31:0]。

对此寄存器的虚拟访问更新 ICH_VMCR_EL2.VBPR0。

属性

ICC_BPR0_EL1 是 64 位寄存器。

字段描述

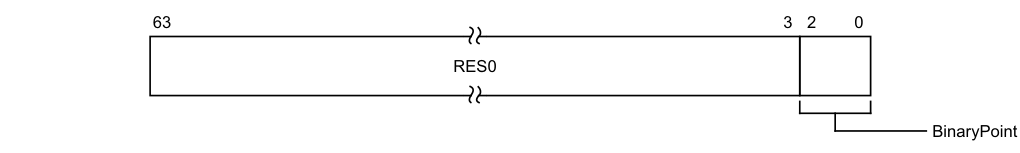

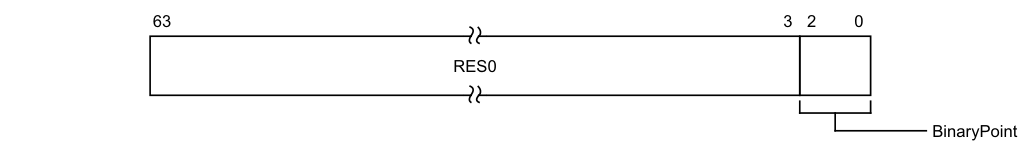

ICC_BPR0_EL1 位分配:

63 3 2 0

RES0

BinaryPoint

位 [63:3]

保留,RES0。

BinaryPoint, 位 [2:0]

此字段的值控制如何将 8 位中断优先级字段分割为组优先级字段(决定中断抢占)和子优先级字段。操作如下:

| 二进制分割点值 | 组优先级字段 | 子优先级字段 | 带二进制分割点的字段 |

|---|---|---|---|

| 0 | [7:1] | [0] | ggggggg.s |

| 1 | [7:2] | [1:0] | gggggg.ss |

| 2 | [7:3] | [2:0] | ggggg.sss |

| 3 | [7:4] | [3:0] | gggg.ssss |

| 4 | [7:5] | [4:0] | ggg.sssss |

| 5 | [7:6] | [5:0] | gg.ssssss |

| 6 | [7] | [6:0] | g.sssssss |

| 7 | 无抢占 | [7:0] | .ssssssss |

在热复位时,此字段复位为架构上的 UNKNOWN 值。

访问 ICC_BPR0_EL1

最小二进制分割点值从实现的优先级位数派生。优先级位数是 IMPLEMENTATION DEFINED,由 ICC_CTLR_EL1.PRIbits 和 ICC_CTLR_EL3.PRIbits 报告。

尝试将二进制分割点字段编程为小于最小值的值会将字段设置为最小值。在复位时,二进制分割点字段是 UNKNOWN。

访问此寄存器使用系统指令编码空间中的以下编码:

MRS , ICC_BPR0_EL1

| op0 | op1 | CRn | CRm | op2 |

|---|---|---|---|---|

| 0b11 | 0b000 | 0b1100 | 0b1000 | 0b011 |

if PSTATE.EL == EL0 then UNDEFINED;

elsif PSTATE.EL == EL1 then

if Halted() && HaveEL(EL3) && EDSCR.SDD == '1' &&

boolean IMPLEMENTATION_DEFINED "EL3 trap priority

when SDD == '1'" && SCR_EL3.FIQ == '1' then UNDEFINED;

elsif ICC_SRE_EL1.SRE == '0' then AArch64.SystemAccessTrap(EL1, 0x18);

elsif EL2Enabled() && ICH_HCR_EL2.TALL0 == '1' then AArch64.SystemAccessTrap(EL2, 0x18);

elsif EL2Enabled() && HCR_EL2.FMO == '1' then

return ICV_BPR0_EL1;

elsif HaveEL(EL3) && SCR_EL3.FIQ == '1' then

if Halted() && EDSCR.SDD == '1' then UNDEFINED;

else AArch64.SystemAccessTrap(EL3, 0x18);

else return ICC_BPR0_EL1;

elsif PSTATE.EL == EL2 then

if Halted() && HaveEL(EL3) && EDSCR.SDD == '1' &&

boolean IMPLEMENTATION_DEFINED "EL3 trap priority

when SDD == '1'" && SCR_EL3.FIQ == '1' then UNDEFINED;

elsif ICC_SRE_EL2.SRE == '0' then AArch64.SystemAccessTrap(EL2, 0x18);

elsif HaveEL(EL3) && SCR_EL3.FIQ == '1' then

if Halted() && EDSCR.SDD == '1' then UNDEFINED;

else AArch64.SystemAccessTrap(EL3, 0x18);

else return ICC_BPR0_EL1;

elsif PSTATE.EL == EL3 then

if ICC_SRE_EL3.SRE == '0' then AArch64.SystemAccessTrap(EL3, 0x18);

else return ICC_BPR0_EL1;

MSR ICC_BPR0_EL1,

| op0 | op1 | CRn | CRm | op2 |

|---|---|---|---|---|

| 0b11 | 0b000 | 0b1100 | 0b1000 | 0b011 |

if PSTATE.EL == EL0 then UNDEFINED;

elsif PSTATE.EL == EL1 then

if Halted() && HaveEL(EL3) && EDSCR.SDD == '1' &&

boolean IMPLEMENTATION_DEFINED "EL3 trap priority

when SDD == '1'" && SCR_EL3.FIQ == '1' then

UNDEFINED;

elsif ICC_SRE_EL1.SRE == '0' then

AArch64.SystemAccessTrap(EL1, 0x18);

elsif EL2Enabled() && ICH_HCR_EL2.TALL0 == '1'

then AArch64.SystemAccessTrap(EL2, 0x18);

elsif EL2Enabled() && HCR_EL2.FMO == '1'

then ICV_BPR0_EL1 = X[t];

elsif HaveEL(EL3) && SCR_EL3.FIQ == '1'

then if Halted() && EDSCR.SDD == '1'

then UNDEFINED;

else AArch64.SystemAccessTrap(EL3, 0x18);

else ICC_BPR0_EL1 = X[t];

elsif PSTATE.EL == EL2

then if Halted() && HaveEL(EL3) && EDSCR.SDD == '1' && boolean IMPLEMENTATION_DEFINED "EL3 trap priority when SDD == '1'" && SCR_EL3.FIQ == '1'

then UNDEFINED;

elsif ICC_SRE_EL2.SRE == '0'

then AArch64.SystemAccessTrap(EL2, 0x18);

elsif HaveEL(EL3) && SCR_EL3.FIQ == '1'

then if Halted() && EDSCR.SDD == '1'

then UNDEFINED;

else AArch64.SystemAccessTrap(EL3, 0x18);

else ICC_BPR0_EL1 = X[t];

elsif PSTATE.EL == EL3

then if ICC_SRE_EL3.SRE == '0'

then AArch64.SystemAccessTrap(EL3, 0x18);

else ICC_BPR0_EL1 = X[t];

12.2.5 ICC_BPR1_EL1, 中断控制器二进制分割点寄存器 1

ICC_BPR1_EL1 特性如下:

目的

定义优先级值字段分割为两部分的点,即组优先级字段和子优先级字段。组优先级字段决定 Group 1 中断抢占。

配置

AArch64 系统寄存器 ICC_BPR1_EL1 位 [31:0] (S) 在架构上映射到 AArch32 系统寄存器 ICC_BPR1[31:0] (S)。

AArch64 系统寄存器 ICC_BPR1_EL1 位 [31:0] (NS) 在架构上映射到 AArch32 系统寄存器 ICC_BPR1[31:0] (NS)。

对此寄存器的虚拟访问更新 ICH_VMCR_EL2.VBPR1。

属性

ICC_BPR1_EL1 是 64 位寄存器。

字段描述

ICC_BPR1_EL1 位分配:

63 3 2 0

RES0

BinaryPoint

位 [63:3]

保留,RES0。

BinaryPoint, 位 [2:0]

如果 GIC 配置为对 Group 0 和 Group 1 中断使用单独的二进制分割点字段,此字段的值控制如何将 8 位中断优先级字段分割为组优先级字段(决定中断抢占)和子优先级字段。有关优先级的更多信息,请参见 优先级分组。

此寄存器非安全副本的最小值是 ICC_BPR0_EL1 最小值 + 1。此寄存器安全副本的最小值是 ICC_BPR0_EL1 的最小值。

如果实现了 EL3 且 ICC_CTLR_EL3.CBPR_EL1S 是 1:

-

当 SCR_EL3.EEL2 是 1 且 HCR_EL2.IMO 是 1 时,在 EL1 的安全访问访问 ICV_BPR1_EL1 的状态。

-

否则,在 EL1 的安全访问访问 ICC_BPR0_EL1 的状态。

如果实现了 EL3 且 ICC_CTLR_EL3.CBPR_EL1NS 是 1,在 EL1 或 EL2 的非安全访问按以下方式行为,取决于 HCR_EL2.IMO 和 SCR_EL3.IRQ 的值:

| HCR_EL2.IMO | SCR_EL3.IRQ | 行为 |

|---|---|---|

| 0b0 | 0b0 | 非安全 EL1 和 EL2 读取返回 ICC_BPR0_EL1+ 1 饱和到 0b111。非安全 EL1 和 EL2 写入被忽略。 |

| 0b0 | 0b1 | 非安全 EL1 和 EL2 访问陷阱到 EL3。 |

| 0b1 | 0b0 | 非安全 EL1 访问影响虚拟中断。非安全 EL2 读取返回 ICC_BPR0_EL1+ 1 饱和到 0b111。非安全 EL2 写入被忽略。 |

| 0b1 | 0b1 | 非安全 EL1 访问影响虚拟中断。非安全 EL2 访问陷阱到 EL3。如果未实现 EL3 且 ICC_CTLR_EL1.CBPR 是 1,在 EL1 或 EL2 的非安全访问按以下方式行为,取决于 HCR_EL2.IMO 的值: |

| HCR_EL2.IMO | 行为 | |

|---|---|---|

| 0b0 | 非安全 EL1 和 EL2 读取返回 ICC_BPR0_EL1+ 1 饱和到 0b111。非安全 EL1 和 EL2 写入被忽略。 | |

| 0b1 | 非安全 EL1 访问影响虚拟中断。非安全 EL2 读取返回 ICC_BPR0_EL1+ 1 饱和到 0b111。非安全 EL2 写入被忽略。 |

在热复位时,此字段复位为架构上的 UNKNOWN 值。

访问 ICC_BPR1_EL1

在复位时,二进制分割点字段是 UNKNOWN。

尝试将二进制分割点字段编程为小于最小值的值会将字段设置为最小值。

访问此寄存器使用系统指令编码空间中的以下编码:

MRS , ICC_BPR1_EL1

| op0 | op1 | CRn | CRm | op2 |

|---|---|---|---|---|

| 0b11 | 0b000 | 0b1100 | 0b1100 | 0b011 |

if PSTATE.EL == EL0 then UNDEFINED;

elsif PSTATE.EL == EL1 then

if Halted() && HaveEL(EL3) && EDSCR.SDD == '1' &&

boolean IMPLEMENTATION_DEFINED "EL3 trap priority

when SDD == '1'" && SCR_EL3.IRQ == '1' then

UNDEFINED;

elsif ICC_SRE_EL1.SRE == '0' then AArch64.SystemAccessTrap(EL1, 0x18);

elsif EL2Enabled() && ICH_HCR_EL2.TALL1 == '1' then AArch64.SystemAccessTrap(EL2, 0x18);

elsif EL2Enabled() && HCR_EL2.IMO == '1' then

return ICV_BPR1_EL1;

elsif HaveEL(EL3) && SCR_EL3.IRQ == '1' then

if Halted() && EDSCR.SDD == '1' then UNDEFINED;

else AArch64.SystemAccessTrap(EL3, 0x18);

elsif HaveEL(EL3) then

if SCR_EL3.NS == '0' then

return ICC_BPR1_EL1_S;

else return ICC_BPR1_EL1_NS;

else return ICC_BPR1_EL1;

elsif PSTATE.EL == EL2 then

if Halted() && HaveEL(EL3) && EDSCR.SDD == '1' &&

boolean IMPLEMENTATION_DEFINED "EL3 trap priority

when SDD == '1'" && SCR_EL3.IRQ == '1' then UNDEFINED;

elsif ICC_SRE_EL2.SRE == '0' then AArch64.SystemAccessTrap(EL2, 0x18);

elsif HaveEL(EL3) && SCR_EL3.IRQ == '1' then

if Halted() && EDSCR.SDD == '1' then UNDEFINED;

else AArch64.SystemAccessTrap(EL3, 0x18);

elsif HaveEL(EL3) then

if SCR_EL3.NS == '0' then

return ICC_BPR1_EL1_S;

else return ICC_BPR1_EL1_NS;

else return ICC_BPR1_EL1;

elsif PSTATE.EL == EL3 then

if ICC_SRE_EL3.SRE == '0' then AArch64.SystemAccessTrap(EL3, 0x18);

else if SCR_EL3.NS == '0' then

return ICC_BPR1_EL1_S;

else return ICC_BPR1_EL1_NS;

MSR ICC_BPR1_EL1,

| op0 | op1 | CRn | CRm | op2 |

|---|---|---|---|---|

| 0b11 | 0b000 | 0b1100 | 0b1100 | 0b011 |

if PSTATE.EL == EL0 then UNDEFINED;

elsif PSTATE.EL == EL1 then

if Halted() && HaveEL(EL3) && EDSCR.SDD == '1' &&

boolean IMPLEMENTATION_DEFINED "EL3 trap priority

when SDD == '1'" && SCR_EL3.IRQ == '1' then UNDEFINED;

elsif ICC_SRE_EL1.SRE == '0' then AArch64.SystemAccessTrap(EL1, 0x18);

elsif EL2Enabled() && ICH_HCR_EL2.TALL1 == '1' then AArch64.SystemAccessTrap(EL2, 0x18);

elsif EL2Enabled() && HCR_EL2.IMO == '1' then ICV_BPR1_EL1 = X[t];

elsif HaveEL(EL3) && SCR_EL3.IRQ == '1' then

if Halted() && EDSCR.SDD == '1' then UNDEFINED;

else AArch64.SystemAccessTrap(EL3, 0x18);

elsif HaveEL(EL3) then

if SCR_EL3.NS == '0' then ICC_BPR1_EL1_S = X[t];

else ICC_BPR1_EL1_NS = X[t];

else

ICC_BPR1_EL1 = X[t];

elsif PSTATE.EL == EL2 then

if Halted() && HaveEL(EL3) && EDSCR.SDD == '1' &&

boolean IMPLEMENTATION_DEFINED "EL3 trap priority

when SDD == '1'" && SCR_EL3.IRQ == '1' then UNDEFINED;

elsif ICC_SRE_EL2.SRE == '0' then AArch64.SystemAccessTrap(EL2, 0x18);

elsif HaveEL(EL3) && SCR_EL3.IRQ == '1' then

if Halted() && EDSCR.SDD == '1' then UNDEFINED;

else AArch64.SystemAccessTrap(EL3, 0x18);

elsif HaveEL(EL3) then

if SCR_EL3.NS == '0' then ICC_BPR1_EL1_S = X[t];

else ICC_BPR1_EL1_NS = X[t];

else ICC_BPR1_EL1 = X[t];

elsif PSTATE.EL == EL3 then

if ICC_SRE_EL3.SRE == '0' then AArch64.SystemAccessTrap(EL3, 0x18);

else if SCR_EL3.NS == '0' then ICC_BPR1_EL1_S = X[t];

else ICC_BPR1_EL1_NS = X[t];

12.2.6 ICC_CTLR_EL1, 中断控制器控制寄存器 (EL1)

ICC_CTLR_EL1 特性如下:

目的

控制 GIC CPU 接口行为的各个方面,并提供关于已实现功能的信息。

配置

AArch64 系统寄存器 ICC_CTLR_EL1 位 [31:0] (S) 在架构上映射到 AArch32 系统寄存器 ICC_CTLR[31:0] (S)。

AArch64 系统寄存器 ICC_CTLR_EL1 位 [31:0] (NS) 在架构上映射到 AArch32 系统寄存器 ICC_CTLR[31:0] (NS)。

属性

ICC_CTLR_EL1 是 64 位寄存器。

字段描述

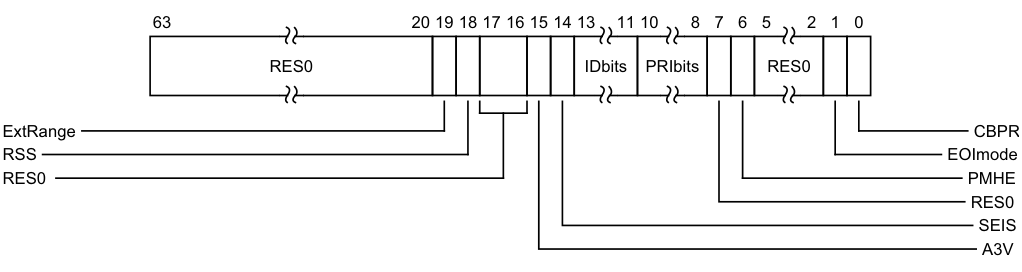

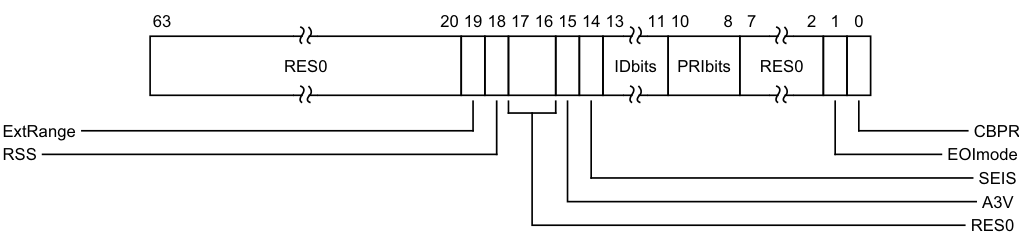

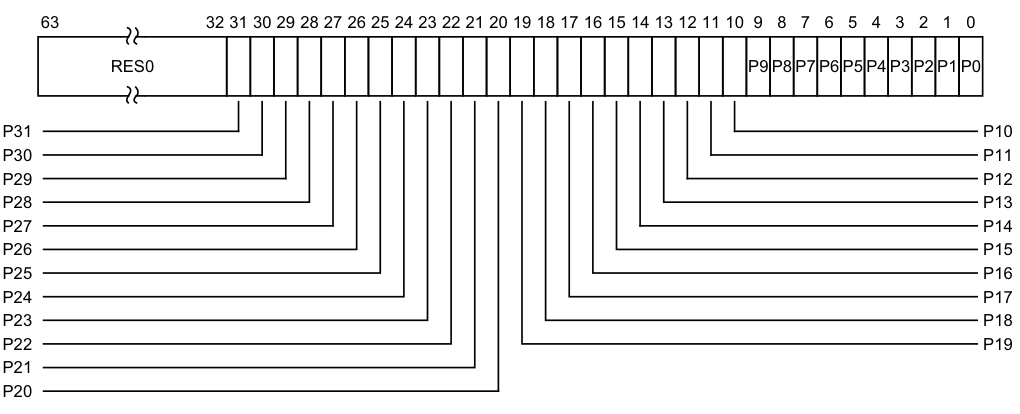

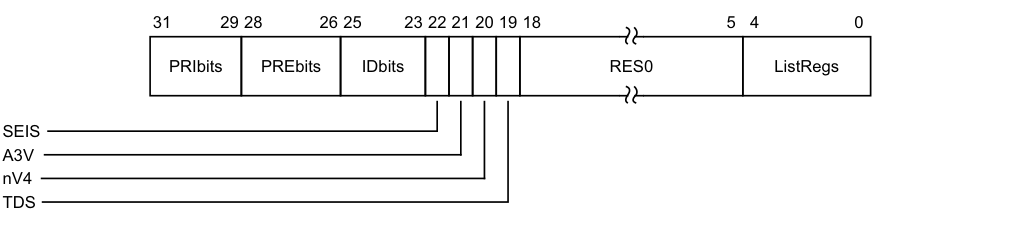

ICC_CTLR_EL1 位分配:

63 20 19 18 17 16 15 14 13 11 10 8 7 6 5 2 1 0

RES0 IDbits PRIbits RES0

ExtRange CBPR

RSS EOImode

RES0 PMHE

RES0

SEIS

A3V

位 [63:20]

保留,RES0。

ExtRange, 位 [19]

扩展 INTID 范围(只读)。

0b0 CPU 接口不支持范围 1024..8191 中的 INTID。

- 如果 IRI 向 CPU 接口传递范围 1024 到 8191 中的中断,行为是 UNPREDICTABLE。

注意 Arm 强烈建议不要将 IRI 配置为向不支持它们的 PE 传递此范围内的中断。

0b1 CPU 接口支持范围 1024..8191 中的 INTID

- 范围 1024..8191 中的所有 INTID 被视为需要去活化。

如果实现了 EL3,ICC_CTLR_EL1.ExtRange 是 ICC_CTLR_EL3.ExtRange 的别名。

RSS, 位 [18]

范围选择器支持。可能的值是:

0b0 支持亲和性级别 0 值为 0 - 15 的定向 SGI。0b1 支持亲和性级别 0 值为 0 - 255 的定向 SGI。

此位是只读的。

位 [17:16]

保留,RES0。

A3V, 位 [15]

亲和性 3 有效。只读,写入被忽略。可能的值是:

0b0 CPU 接口逻辑只支持 SGI 生成系统寄存器中亲和性 3 的零值。0b1 CPU 接口逻辑支持 SGI 生成系统寄存器中亲和性 3 的非零值。

如果实现了 EL3,此位是 ICC_CTLR_EL3.A3V 的别名。

SEIS, 位 [14]

SEI 支持。只读,写入被忽略。指示 CPU 接口是否支持 SEI 的本地生成:

0b0 CPU 接口逻辑不支持 SEI 的本地生成。0b1 CPU 接口逻辑支持 SEI 的本地生成。

如果实现了 EL3,此位是 ICC_CTLR_EL3.SEIS 的别名。

IDbits, 位 [13:11]

标识符位。只读,写入被忽略。支持的物理中断标识符位数:

0b000 16 位。0b001 24 位。所有其他值是保留的。

如果实现了 EL3,此字段是 ICC_CTLR_EL3.IDbits 的别名。

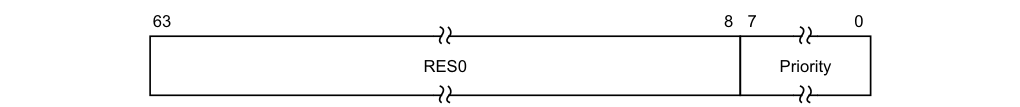

PRIbits, 位 [10:8]

优先级位。只读,写入被忽略。实现的优先级位数减一。

支持两个安全状态的实现必须实现至少 32 级物理优先级(5 个优先级位)。

只支持单一安全状态的实现必须实现至少 16 级物理优先级(4 个优先级位)。

注意

无论访问的安全状态或 GICD_CTLR.DS 的值如何,此字段始终返回实现的优先级位数。

对于物理访问,此字段确定 ICC_BPR0_EL1 的最小值。

如果实现了 EL3,物理访问返回 ICC_CTLR_EL3.PRIbits 的值。

如果未实现 EL3,物理访问返回此字段的值。

位 [7]

保留,RES0。

PMHE, 位 [6]

优先级掩码提示启用。控制是否将优先级掩码寄存器用作中断分发的提示:

0b0 禁用将 ICC_PMR_EL1 用作中断分发的提示。0b1 启用将 ICC_PMR_EL1 用作中断分发的提示。

如果实现了 EL3,此位是 ICC_CTLR_EL3.PMHE 的别名。此位是否可以作为对此寄存器访问的一部分写入取决于 GICD_CTLR.DS 的值:

-

如果 GICD_CTLR.DS == 0,此位是只读的。

-

如果 GICD_CTLR.DS == 1,此位是读/写的。

-

如果未实现 EL3,此位是只读还是读/写是 IMPLEMENTATION DEFINED:

-

如果此位是只读的,实现可以选择使此字段为 RAZ/WI 或 RAO/WI。

-

如果此位是读/写的,它复位为零。

位 [5:2]

保留,RES0。

EOImode, 位 [1]

当前安全状态的 EOI 模式。控制写入中断结束寄存器是否也去活化中断:

0b0 ICC_EOIR0_EL1 和 ICC_EOIR1_EL1 提供优先级下降和中断去活化功能。访问 ICC_DIR_EL1 是 UNPREDICTABLE。0b1 ICC_EOIR0_EL1 和 ICC_EOIR1_EL1 只提供优先级下降功能。ICC_DIR_EL1 提供中断去活化功能。

安全 ICC_CTLR_EL1.EOImode 是 ICC_CTLR_EL3.EOImode_EL1S 的别名。

非安全 ICC_CTLR_EL1.EOImode 是 ICC_CTLR_EL3.EOImode_EL1NS 的别名

CBPR, 位 [0]

公共二进制分割点寄存器。控制是否对 Group 0 和 Group 1 中断的中断抢占使用相同的寄存器:

0b0 ICC_BPR0_EL1 仅决定 Group 0 中断的抢占组。ICC_BPR1_EL1 决定 Group 1 中断的抢占组。

0b1 ICC_BPR0_EL1 决定 Group 0 和 Group 1 中断的抢占组。

如果实现了 EL3:

-

此位是 ICC_CTLR_EL3.CBPR_EL1{S,NS} 的别名,其中 S 或 NS 对应当前安全状态。

-

如果 GICD_CTLR.DS == 0,此位是只读的。

-

如果 GICD_CTLR.DS == 1,此位是读/写的。

如果未实现 EL3,此位是读/写的。

在热复位时,此字段复位为架构上的 UNKNOWN 值。

访问 ICC_CTLR_EL1

访问此寄存器使用系统指令编码空间中的以下编码:

MRS , ICC_CTLR_EL1

| op0 | op1 | CRn | CRm | op2 |

|---|---|---|---|---|

| 0b11 | 0b000 | 0b1100 | 0b1100 | 0b100 |

if PSTATE.EL == EL0 then UNDEFINED;

elsif PSTATE.EL == EL1 then

if Halted() && HaveEL(EL3) && EDSCR.SDD == '1' &&

boolean IMPLEMENTATION_DEFINED "EL3 trap priority

when SDD == '1'" && SCR_EL3.<IRQ,FIQ> == '11' then

UNDEFINED;

elsif ICC_SRE_EL1.SRE == '0'

then AArch64.SystemAccessTrap(EL1, 0x18);

elsif EL2Enabled() && ICH_HCR_EL2.TC == '1'

then AArch64.SystemAccessTrap(EL2, 0x18);

elsif EL2Enabled() && HCR_EL2.FMO == '1'

then return ICV_CTLR_EL1;

elsif EL2Enabled() && HCR_EL2.IMO == '1'

then return ICV_CTLR_EL1;

elsif HaveEL(EL3) && SCR_EL3.<IRQ,FIQ> == '11'

then if Halted() && EDSCR.SDD == '1'

then UNDEFINED;

else AArch64.SystemAccessTrap(EL3, 0x18);

elsif HaveEL(EL3)

then if SCR_EL3.NS == '0'

then return ICC_CTLR_EL1_S;

else return ICC_CTLR_EL1_NS;

else return ICC_CTLR_EL1;

elsif PSTATE.EL == EL2

then if Halted() && HaveEL(EL3) && EDSCR.SDD == '1' && boolean IMPLEMENTATION_DEFINED "EL3 trap priority when SDD == '1'" && SCR_EL3.<IRQ,FIQ> == '11'

then UNDEFINED;

elsif ICC_SRE_EL2.SRE == '0'

then AArch64.SystemAccessTrap(EL2, 0x18);

elsif HaveEL(EL3) && SCR_EL3.<IRQ,FIQ> == '11'

then if Halted() && EDSCR.SDD == '1'

then UNDEFINED;

else AArch64.SystemAccessTrap(EL3, 0x18);

elsif HaveEL(EL3)

then if SCR_EL3.NS == '0'

then return ICC_CTLR_EL1_S;

else return ICC_CTLR_EL1_NS;

else return ICC_CTLR_EL1;

elsif PSTATE.EL == EL3

then if ICC_SRE_EL3.SRE == '0'

then AArch64.SystemAccessTrap(EL3, 0x18);

else if SCR_EL3.NS == '0'

then return ICC_CTLR_EL1_S;

else return ICC_CTLR_EL1_NS;

MSR ICC_CTLR_EL1,

| op0 | op1 | CRn | CRm | op2 |

|---|---|---|---|---|

| 0b11 | 0b000 | 0b1100 | 0b1100 | 0b100 |

if PSTATE.EL == EL0 then UNDEFINED;

elsif PSTATE.EL == EL1 then

if Halted() && HaveEL(EL3) && EDSCR.SDD == '1' &&

boolean IMPLEMENTATION_DEFINED "EL3 trap priority

when SDD == '1'" && SCR_EL3.<IRQ,FIQ> == '11' then

UNDEFINED;

elsif ICC_SRE_EL1.SRE == '0'

then AArch64.SystemAccessTrap(EL1, 0x18);

elsif EL2Enabled() && ICH_HCR_EL2.TC == '1'

then AArch64.SystemAccessTrap(EL2, 0x18);

elsif EL2Enabled() && HCR_EL2.FMO == '1' then

ICV_CTLR_EL1 = X[t];

elsif EL2Enabled() && HCR_EL2.IMO == '1'

then ICV_CTLR_EL1 = X[t];

elsif HaveEL(EL3) && SCR_EL3.<IRQ,FIQ> == '11'

then if Halted() && EDSCR.SDD == '1'

then UNDEFINED;

else AArch64.SystemAccessTrap(EL3, 0x18);

elsif HaveEL(EL3)

then if SCR_EL3.NS == '0'

then ICC_CTLR_EL1_S = X[t];

else ICC_CTLR_EL1_NS = X[t];

else ICC_CTLR_EL1 = X[t];

elsif PSTATE.EL == EL2

then if Halted() && HaveEL(EL3) && EDSCR.SDD == '1' && boolean IMPLEMENTATION_DEFINED "EL3 trap priority when SDD == '1'" && SCR_EL3.<IRQ,FIQ> == '11'

then UNDEFINED;

elsif ICC_SRE_EL2.SRE == '0'

then AArch64.SystemAccessTrap(EL2, 0x18);

elsif HaveEL(EL3) && SCR_EL3.<IRQ,FIQ> == '11'

then if Halted() && EDSCR.SDD == '1'

then UNDEFINED;

else AArch64.SystemAccessTrap(EL3, 0x18);

elsif HaveEL(EL3)

then if SCR_EL3.NS == '0'

then ICC_CTLR_EL1_S = X[t];

else ICC_CTLR_EL1_NS = X[t];

else ICC_CTLR_EL1 = X[t];

elsif PSTATE.EL == EL3

then if ICC_SRE_EL3.SRE == '0'

then AArch64.SystemAccessTrap(EL3, 0x18);

else if SCR_EL3.NS == '0'

then ICC_CTLR_EL1_S = X[t];

else ICC_CTLR_EL1_NS = X[t];

```## 12.3 虚拟寄存器的AArch64系统寄存器描述

本节按寄存器名称顺序描述每个虚拟AArch64 GIC系统寄存器。ICV前缀表示一个虚拟GIC CPU接口系统寄存器。每个AArch64系统寄存器描述都包含对提供相同功能的AArch32寄存器的引用。

除非另有说明,GIC系统寄存器的位分配与等效的GICC_*和GICV_*内存映射寄存器相同。

ICV_*寄存器只能在EL1访问,并且只有在当前安全状态下EL2已启用时才可访问。访问编码是映射到ICC_*寄存器还是等效的ICV_*寄存器由HCR_EL2决定,请参见第6章_虚拟中断处理和优先级_。等效的虚拟接口内存映射寄存器在_GIC虚拟CPU接口寄存器描述_中描述。

虚拟寄存器的编码与物理寄存器相同,请参见表12-21。

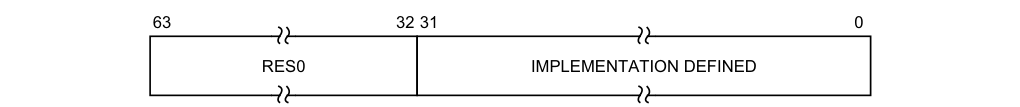

## 12.3.1 ICV_AP0R<n>_EL1,中断控制器虚拟活动优先级0组寄存器,n = 0 - 3

ICV_AP0R<n>_EL1的特性:

## 目的

提供虚拟0组活动优先级的信息。

## 配置

AArch64系统寄存器ICV_AP0R<n>_EL1的位[31:0]在架构上映射到AArch32系统寄存器ICV_AP0R<n>[31:0]。

## 属性

ICV_AP0R<n>_EL1是一个64位寄存器。

## 字段描述

ICV_AP0R<n>_EL1的位分配:

63 32 31 0<br>RES0 IMPLEMENTATION DEFINED

## 位[63:32]

保留,RES0。

## IMPLEMENTATION DEFINED,位[31:0]

## IMPLEMENTATION DEFINED。

在热复位时,此字段复位为架构上未知的值。

这些寄存器的内容是IMPLEMENTATION DEFINED的,有一个架构要求是值0x00000000与没有活动中断的状态一致。

## 访问ICV_AP0R<n>_EL1

使用除寄存器最后读取值以外的任何值(或当没有0组活动优先级时为0x00000000)写入这些寄存器,可能导致虚拟中断优先级系统的UNPREDICTABLE行为,造成:

- 应该抢占执行的中断不抢占执行。

- 不应该抢占执行的中断抢占执行。

ICV_AP0R1_EL1仅在支持6个或更多优先级位的实现中实现。

ICV_AP0R2_EL1和ICV_AP0R3_EL1仅在支持7个优先级位的实现中实现。未实现的寄存器为UNDEFINED。

按除以下顺序外的任何顺序写入活动优先级寄存器,可能导致中断优先级系统的UNPREDICTABLE行为:

- ICV_AP0R<n>_EL1。

- ICV_AP1R<n>_EL1。

访问此寄存器使用系统指令编码空间中的以下编码:

## _**MRS <Xt>, ICC_AP0R<n>_EL1**_

| **op0** | **op1** | **CRn** | **CRm** | **op2** |

|---|---|---|---|---|

| 0b11 | 0b000 | 0b1100 | 0b1000 | 0b1:n[1:0] |

if PSTATE.EL == EL0 then UNDEFINED; elsif PSTATE.EL == EL1 then if Halted() && HaveEL(EL3) && EDSCR.SDD == ‘1’ && boolean IMPLEMENTATION_DEFINED “EL3 trap priority when SDD == ‘1’” && SCR_EL3.FIQ == ‘1’ then UNDEFINED; elsif ICC_SRE_EL1.SRE == ‘0’ then AArch64.SystemAccessTrap(EL1, 0x18); elsif EL2Enabled() && ICH_HCR_EL2.TALL0 == ‘1’ then AArch64.SystemAccessTrap(EL2, 0x18); elsif EL2Enabled() && HCR_EL2.FMO == ‘1’ then return ICV_AP0R_EL1[UInt(op2<1:0>)]; elsif HaveEL(EL3) && SCR_EL3.FIQ == ‘1’ then if Halted() && EDSCR.SDD == ‘1’ then UNDEFINED; else AArch64.SystemAccessTrap(EL3, 0x18); else return ICC_AP0R_EL1[UInt(op2<1:0>)]; elsif PSTATE.EL == EL2 then if Halted() && HaveEL(EL3) && EDSCR.SDD == ‘1’ && boolean IMPLEMENTATION_DEFINED “EL3 trap priority when SDD == ‘1’” && SCR_EL3.FIQ == ‘1’ then

UNDEFINED; elsif ICC_SRE_EL2.SRE == ‘0’ then AArch64.SystemAccessTrap(EL2, 0x18); elsif HaveEL(EL3) && SCR_EL3.FIQ == ‘1’ then if Halted() && EDSCR.SDD == ‘1’ then UNDEFINED; else AArch64.SystemAccessTrap(EL3, 0x18); else return ICC_AP0R_EL1[UInt(op2<1:0>)]; elsif PSTATE.EL == EL3 then if ICC_SRE_EL3.SRE == ‘0’ then AArch64.SystemAccessTrap(EL3, 0x18); else return ICC_AP0R_EL1[UInt(op2<1:0>)];

## _**MSR ICC_AP0R<n>_EL1, <Xt>**_

| **op0** | **op1** | **CRn** | **CRm** | **op2** |

|---|---|---|---|---|

| 0b11 | 0b000 | 0b1100 | 0b1000 | 0b1:n[1:0] |

if PSTATE.EL == EL0 then UNDEFINED; elsif PSTATE.EL == EL1 then if Halted() && HaveEL(EL3) && EDSCR.SDD == ‘1’ && boolean IMPLEMENTATION_DEFINED “EL3 trap priority when SDD == ‘1’” && SCR_EL3.FIQ == ‘1’ then

UNDEFINED; elsif ICC_SRE_EL1.SRE == ‘0’ then AArch64.SystemAccessTrap(EL1, 0x18); elsif EL2Enabled() && ICH_HCR_EL2.TALL0 == ‘1’ then AArch64.SystemAccessTrap(EL2, 0x18); elsif EL2Enabled() && HCR_EL2.FMO == ‘1’ then ICV_AP0R_EL1[UInt(op2<1:0>)] = X[t]; elsif HaveEL(EL3) && SCR_EL3.FIQ == ‘1’ then

if Halted() && EDSCR.SDD == ‘1’ then UNDEFINED; else AArch64.SystemAccessTrap(EL3, 0x18); else ICC_AP0R_EL1[UInt(op2<1:0>)] = X[t]; elsif PSTATE.EL == EL2 then if Halted() && HaveEL(EL3) && EDSCR.SDD == ‘1’ && boolean IMPLEMENTATION_DEFINED “EL3 trap priority when SDD == ‘1’” && SCR_EL3.FIQ == ‘1’ then UNDEFINED; elsif ICC_SRE_EL2.SRE == ‘0’ then AArch64.SystemAccessTrap(EL2, 0x18); elsif HaveEL(EL3) && SCR_EL3.FIQ == ‘1’ then if Halted() && EDSCR.SDD == ‘1’ then UNDEFINED; else AArch64.SystemAccessTrap(EL3, 0x18); else ICC_AP0R_EL1[UInt(op2<1:0>)] = X[t]; elsif PSTATE.EL == EL3 then if ICC_SRE_EL3.SRE == ‘0’ then AArch64.SystemAccessTrap(EL3, 0x18); else ICC_AP0R_EL1[UInt(op2<1:0>)] = X[t];

## 12.3.2 ICV_AP1R<n>_EL1,中断控制器虚拟活动优先级1组寄存器,n = 0 - 3

ICV_AP1R<n>_EL1的特性:

## 目的

提供虚拟1组活动优先级的信息。

## 配置

AArch64系统寄存器ICV_AP1R<n>_EL1的位[31:0]在架构上映射到AArch32系统寄存器ICV_AP1R<n>[31:0]。

## 属性

ICV_AP1R<n>_EL1是一个64位寄存器。

## 字段描述

ICV_AP1R<n>_EL1的位分配:

63 32 31 0<br>RES0 IMPLEMENTATION DEFINED

## 位[63:32]

保留,RES0。

## IMPLEMENTATION DEFINED,位[31:0]

IMPLEMENTATION DEFINED。

在热复位时,此字段复位为架构上未知的值。

这些寄存器的内容是IMPLEMENTATION DEFINED的,有一个架构要求是值0x00000000与没有活动中断的状态一致。

## 访问ICV_AP1R<n>_EL1

使用除寄存器最后读取值以外的任何值(或当没有1组活动优先级时为0x00000000)写入这些寄存器,可能导致虚拟中断优先级系统的UNPREDICTABLE行为,造成:

- 应该抢占执行的中断不抢占执行。

- 不应该抢占执行的中断抢占执行。

ICV_AP1R1_EL1仅在支持6个或更多优先级位的实现中实现。

ICV_AP1R2_EL1和ICV_AP1R3_EL1仅在支持7个优先级位的实现中实现。未实现的寄存器为UNDEFINED。

按除以下顺序外的任何顺序写入活动优先级寄存器,可能导致中断优先级系统的UNPREDICTABLE行为:

- ICV_AP0R<n>_EL1。

- ICV_AP1R<n>_EL1。

访问此寄存器使用系统指令编码空间中的以下编码:

## _**MRS <Xt>, ICC_AP1R<n>_EL1**_

| **op0** | **op1** | **CRn** | **CRm** | **op2** |

|---|---|---|---|---|

| 0b11 | 0b000 | 0b1100 | 0b1001 | 0b0:n[1:0] |

if PSTATE.EL == EL0 then UNDEFINED; elsif PSTATE.EL == EL1 then if Halted() && HaveEL(EL3) && EDSCR.SDD == ‘1’ && boolean IMPLEMENTATION_DEFINED “EL3 trap priority when SDD == ‘1’” && SCR_EL3.IRQ == ‘1’ then UNDEFINED; elsif ICC_SRE_EL1.SRE == ‘0’ then AArch64.SystemAccessTrap(EL1, 0x18); elsif EL2Enabled() && ICH_HCR_EL2.TALL1 == ‘1’ then AArch64.SystemAccessTrap(EL2, 0x18); elsif EL2Enabled() && HCR_EL2.IMO == ‘1’ then return ICV_AP1R_EL1[UInt(op2<1:0>)]; elsif HaveEL(EL3) && SCR_EL3.IRQ == ‘1’ then if Halted() && EDSCR.SDD == ‘1’ then UNDEFINED; else AArch64.SystemAccessTrap(EL3, 0x18); elsif HaveEL(EL3) then if SCR_EL3.NS == ‘0’ then return ICC_AP1R_EL1_S[UInt(op2<1:0>)]; else return ICC_AP1R_EL1_NS[UInt(op2<1:0>)]; else return ICC_AP1R_EL1[UInt(op2<1:0>)]; elsif PSTATE.EL == EL2 then if Halted() && HaveEL(EL3) && EDSCR.SDD == ‘1’ && boolean IMPLEMENTATION_DEFINED “EL3 trap priority when SDD == ‘1’” && SCR_EL3.IRQ == ‘1’ then UNDEFINED; elsif ICC_SRE_EL2.SRE == ‘0’ then AArch64.SystemAccessTrap(EL2, 0x18); elsif HaveEL(EL3) && SCR_EL3.IRQ == ‘1’ then if Halted() && EDSCR.SDD == ‘1’ then UNDEFINED; else AArch64.SystemAccessTrap(EL3, 0x18); elsif HaveEL(EL3) then if SCR_EL3.NS == ‘0’ then return ICC_AP1R_EL1_S[UInt(op2<1:0>)]; else return ICC_AP1R_EL1_NS[UInt(op2<1:0>)]; else return ICC_AP1R_EL1[UInt(op2<1:0>)]; elsif PSTATE.EL == EL3 then if ICC_SRE_EL3.SRE == ‘0’ then AArch64.SystemAccessTrap(EL3, 0x18); else if SCR_EL3.NS == ‘0’ then return ICC_AP1R_EL1_S[UInt(op2<1:0>)]; else return ICC_AP1R_EL1_NS[UInt(op2<1:0>)];

## _**MSR ICC_AP1R<n>_EL1, <Xt>**_

| **op0** | **op1** | **CRn** | **CRm** | **op2** |

|---|---|---|---|---|

| 0b11 | 0b000 | 0b1100 | 0b1001 | 0b0:n[1:0] |

if PSTATE.EL == EL0 then UNDEFINED; elsif PSTATE.EL == EL1 then if Halted() && HaveEL(EL3) && EDSCR.SDD == ‘1’ && boolean IMPLEMENTATION_DEFINED “EL3 trap priority when SDD == ‘1’” && SCR_EL3.IRQ == ‘1’ then UNDEFINED; elsif ICC_SRE_EL1.SRE == ‘0’ then AArch64.SystemAccessTrap(EL1, 0x18); elsif EL2Enabled() && ICH_HCR_EL2.TALL1 == ‘1’ then AArch64.SystemAccessTrap(EL2, 0x18); elsif EL2Enabled() && HCR_EL2.IMO == ‘1’ then ICV_AP1R_EL1[UInt(op2<1:0>)] = X[t]; elsif HaveEL(EL3) && SCR_EL3.IRQ == ‘1’ then if Halted() && EDSCR.SDD == ‘1’ then UNDEFINED; else AArch64.SystemAccessTrap(EL3, 0x18); elsif HaveEL(EL3) then if SCR_EL3.NS == ‘0’ then ICC_AP1R_EL1_S[UInt(op2<1:0>)] = X[t]; else ICC_AP1R_EL1_NS[UInt(op2<1:0>)] = X[t]; else ICC_AP1R_EL1[UInt(op2<1:0>)] = X[t]; elsif PSTATE.EL == EL2 then if Halted() && HaveEL(EL3) && EDSCR.SDD == ‘1’ && boolean IMPLEMENTATION_DEFINED “EL3 trap priority when SDD == ‘1’” && SCR_EL3.IRQ == ‘1’ then UNDEFINED; elsif ICC_SRE_EL2.SRE == ‘0’ then AArch64.SystemAccessTrap(EL2, 0x18); elsif HaveEL(EL3) && SCR_EL3.IRQ == ‘1’ then if Halted() && EDSCR.SDD == ‘1’ then UNDEFINED; else AArch64.SystemAccessTrap(EL3, 0x18); elsif HaveEL(EL3) then if SCR_EL3.NS == ‘0’ then ICC_AP1R_EL1_S[UInt(op2<1:0>)] = X[t]; else ICC_AP1R_EL1_NS[UInt(op2<1:0>)] = X[t]; else ICC_AP1R_EL1[UInt(op2<1:0>)] = X[t]; elsif PSTATE.EL == EL3 then if ICC_SRE_EL3.SRE == ‘0’ then AArch64.SystemAccessTrap(EL3, 0x18); else if SCR_EL3.NS == ‘0’ then ICC_AP1R_EL1_S[UInt(op2<1:0>)] = X[t]; else ICC_AP1R_EL1_NS[UInt(op2<1:0>)] = X[t];

## 12.3.3 ICV_BPR0_EL1,中断控制器虚拟二进制点寄存器0

ICV_BPR0_EL1的特性:

## 目的

定义优先级值字段分为两部分的点,即组优先级字段和子优先级字段。组优先级字段确定虚拟0组中断抢占。

## 配置

AArch64系统寄存器ICV_BPR0_EL1的位[31:0]在架构上映射到AArch32系统寄存器ICV_BPR0[31:0]。

## 属性

ICV_BPR0_EL1是一个64位寄存器。

## 字段描述

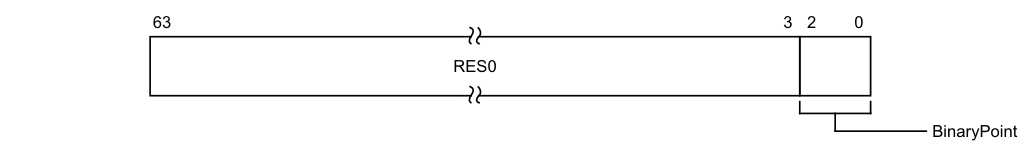

ICV_BPR0_EL1的位分配:

63 3 2 0<br>RES0<br>BinaryPoint

## 位[63:3]

保留,RES0。

## BinaryPoint,位[2:0]

此字段的值控制8位中断优先级字段如何分为组优先级字段(确定中断抢占)和子优先级字段。按以下方式进行:

| **二进制点值** | **组优先级字段** | **子优先级字段** | **带二进制点的字段** |

|---|---|---|---|

| 0 | [7:1] | [0] | ggggggg.s |

| 1 | [7:2] | [1:0] | gggggg.ss |

| 2 | [7:3] | [2:0] | ggggg.sss |

| 3 | [7:4] | [3:0] | gggg.ssss |

| 4 | [7:5] | [4:0] | ggg.sssss |

| 5 | [7:6] | [5:0] | gg.ssssss |

| 6 | [7] | [6:0] | g.sssssss |

| 7 | 无抢占 | [7:0] | .ssssssss |

在热复位时,此字段复位为架构上未知的值。

## 访问ICV_BPR0_EL1

最小二进制点值由实现的抢占位数量派生,如下表所示:

| **实现的抢占位数量** | **BPR0的最小值** |

|---|---|

| 7 | 0 |

| 6 | 1 |

| 5 | 2 |

实现的抢占位数量由ICH_VTR_EL2.PREbits指示。

尝试将二进制点字段编程为小于最小值的值会将字段设置为最小值。在复位时,二进制点字段为UNKNOWN。

访问此寄存器使用系统指令编码空间中的以下编码:

## _**MRS <Xt>, ICC_BPR0_EL1**_

| **op0** | **op1** | **CRn** | **CRm** | **op2** |

|---|---|---|---|---|

| 0b11 | 0b000 | 0b1100 | 0b1000 | 0b011 |

if PSTATE.EL == EL0 then UNDEFINED; elsif PSTATE.EL == EL1 then if Halted() && HaveEL(EL3) && EDSCR.SDD == ‘1’ && boolean IMPLEMENTATION_DEFINED “EL3 trap priority when SDD == ‘1’” && SCR_EL3.FIQ == ‘1’ then

UNDEFINED; elsif ICC_SRE_EL1.SRE == ‘0’ then AArch64.SystemAccessTrap(EL1, 0x18); elsif EL2Enabled() && ICH_HCR_EL2.TALL0 == ‘1’ then AArch64.SystemAccessTrap(EL2, 0x18); elsif EL2Enabled() && HCR_EL2.FMO == ‘1’ then return ICV_BPR0_EL1; elsif HaveEL(EL3) && SCR_EL3.FIQ == ‘1’ then if Halted() && EDSCR.SDD == ‘1’ then UNDEFINED; else AArch64.SystemAccessTrap(EL3, 0x18); else return ICC_BPR0_EL1; elsif PSTATE.EL == EL2 then if Halted() && HaveEL(EL3) && EDSCR.SDD == ‘1’ && boolean IMPLEMENTATION_DEFINED “EL3 trap priority when SDD == ‘1’” && SCR_EL3.FIQ == ‘1’ then UNDEFINED; elsif ICC_SRE_EL2.SRE == ‘0’ then AArch64.SystemAccessTrap(EL2, 0x18); elsif HaveEL(EL3) && SCR_EL3.FIQ == ‘1’ then if Halted() && EDSCR.SDD == ‘1’ then UNDEFINED; else AArch64.SystemAccessTrap(EL3, 0x18); else return ICC_BPR0_EL1; elsif PSTATE.EL == EL3 then if ICC_SRE_EL3.SRE == ‘0’ then AArch64.SystemAccessTrap(EL3, 0x18); else return ICC_BPR0_EL1;

## _**MSR ICC_BPR0_EL1, <Xt>**_

| **op0** | **op1** | **CRn** | **CRm** | **op2** |

|---|---|---|---|---|

| 0b11 | 0b000 | 0b1100 | 0b1000 | 0b011 |

if PSTATE.EL == EL0 then UNDEFINED; elsif PSTATE.EL == EL1 then if Halted() && HaveEL(EL3) && EDSCR.SDD == ‘1’ && boolean IMPLEMENTATION_DEFINED “EL3 trap priority when SDD == ‘1’” && SCR_EL3.FIQ == ‘1’ then UNDEFINED; elsif ICC_SRE_EL1.SRE == ‘0’ then AArch64.SystemAccessTrap(EL1, 0x18); elsif EL2Enabled() && ICH_HCR_EL2.TALL0 == ‘1’ then AArch64.SystemAccessTrap(EL2, 0x18); elsif EL2Enabled() && HCR_EL2.FMO == ‘1’ then ICV_BPR0_EL1 = X[t]; elsif HaveEL(EL3) && SCR_EL3.FIQ == ‘1’ then if Halted() && EDSCR.SDD == ‘1’ then UNDEFINED; else AArch64.SystemAccessTrap(EL3, 0x18); else ICC_BPR0_EL1 = X[t]; elsif PSTATE.EL == EL2 then if Halted() && HaveEL(EL3) && EDSCR.SDD == ‘1’ && boolean IMPLEMENTATION_DEFINED “EL3 trap priority when SDD == ‘1’” && SCR_EL3.FIQ == ‘1’ then UNDEFINED; elsif ICC_SRE_EL2.SRE == ‘0’ then AArch64.SystemAccessTrap(EL2, 0x18); elsif HaveEL(EL3) && SCR_EL3.FIQ == ‘1’ then if Halted() && EDSCR.SDD == ‘1’ then UNDEFINED; else AArch64.SystemAccessTrap(EL3, 0x18); else ICC_BPR0_EL1 = X[t]; elsif PSTATE.EL == EL3 then if ICC_SRE_EL3.SRE == ‘0’ then AArch64.SystemAccessTrap(EL3, 0x18); else ICC_BPR0_EL1 = X[t];

## 12.3.4 ICV_BPR1_EL1,中断控制器虚拟二进制点寄存器1

ICV_BPR1_EL1的特性:

## 目的

定义优先级值字段分为两部分的点,即组优先级字段和子优先级字段。组优先级字段确定虚拟1组中断抢占。

## 配置

AArch64系统寄存器ICV_BPR1_EL1的位[31:0]在架构上映射到AArch32系统寄存器ICV_BPR1[31:0]。

## 属性

ICV_BPR1_EL1是一个64位寄存器。

## 字段描述

ICV_BPR1_EL1的位分配:

63 3 2 0<br>RES0<br>BinaryPoint

## 位[63:3]

保留,RES0。

## BinaryPoint,位[2:0]

如果GIC被配置为对虚拟0组和虚拟1组中断使用单独的二进制点字段,则此字段的值控制8位中断优先级字段如何分为组优先级字段(确定中断抢占)和子优先级字段。按以下方式进行:

## 二进制点值 组优先级字段 子优先级字段 带二进制点的字段

| 0 | - | - | - |

|---|---|---|---|

| 1 | [7:1] | [0] | ggggggg.s |

| 2 | [7:2] | [1:0] | gggggg.ss |

| 3 | [7:3] | [2:0] | ggggg.sss |

| 4 | [7:4] | [3:0] | gggg.ssss |

| 5 | [7:5] | [4:0] | ggg.sssss |

| 6 | [7:6] | [5:0] | gg.ssssss |

| 7 | [7] | [6:0] | g.sssssss |

向此字段写入0将把此字段设置为其复位值。

如果ICV_CTLR_EL1.CBPR设置为1,Non-secure EL1读取返回ICV_BPR0_EL1 + 1饱和到0b111。Non-secure EL1写入被忽略。

如果ICV_CTLR_EL1.CBPR设置为1,Secure EL1读取返回ICV_BPR0_EL1。Secure EL1写入修改ICV_BPR0_EL1。

在热复位时,此字段复位为架构上未知的值。

## 访问ICV_BPR1_EL1

对于Non-secure写入,此字段的最小值是ICH_VMCR_EL2.VBPR0的最小值加一。

对于Secure写入,此字段的最小值是ICH_VMCR_EL2.VBPR0的最小值。

尝试将二进制点字段编程为小于最小值的值会将字段设置为最小值。在复位时,二进制点字段为UNKNOWN。

访问此寄存器使用系统指令编码空间中的以下编码:

## _**MRS <Xt>, ICC_BPR1_EL1**_

| **op0** | **op1** | **CRn** | **CRm** | **op2** |

|---|---|---|---|---|

| 0b11 | 0b000 | 0b1100 | 0b1100 | 0b011 |

if PSTATE.EL == EL0 then UNDEFINED; elsif PSTATE.EL == EL1 then if Halted() && HaveEL(EL3) && EDSCR.SDD == ‘1’ && boolean IMPLEMENTATION_DEFINED “EL3 trap priority when SDD == ‘1’” && SCR_EL3.IRQ == ‘1’ then UNDEFINED; elsif ICC_SRE_EL1.SRE == ‘0’ then AArch64.SystemAccessTrap(EL1, 0x18); elsif EL2Enabled() && ICH_HCR_EL2.TALL1 == ‘1’ then AArch64.SystemAccessTrap(EL2, 0x18); elsif EL2Enabled() && HCR_EL2.IMO == ‘1’ then return ICV_BPR1_EL1; elsif HaveEL(EL3) && SCR_EL3.IRQ == ‘1’ then if Halted() && EDSCR.SDD == ‘1’ then UNDEFINED; else AArch64.SystemAccessTrap(EL3, 0x18); elsif HaveEL(EL3) then if SCR_EL3.NS == ‘0’ then return ICC_BPR1_EL1_S; else return ICC_BPR1_EL1_NS; else return ICC_BPR1_EL1; elsif PSTATE.EL == EL2 then if Halted() && HaveEL(EL3) && EDSCR.SDD == ‘1’ && boolean IMPLEMENTATION_DEFINED “EL3 trap priority when SDD == ‘1’” && SCR_EL3.IRQ == ‘1’ then UNDEFINED; elsif ICC_SRE_EL2.SRE == ‘0’ then AArch64.SystemAccessTrap(EL2, 0x18); elsif HaveEL(EL3) && SCR_EL3.IRQ == ‘1’ then if Halted() && EDSCR.SDD == ‘1’ then UNDEFINED; else AArch64.SystemAccessTrap(EL3, 0x18); elsif HaveEL(EL3) then if SCR_EL3.NS == ‘0’ then return ICC_BPR1_EL1_S; else return ICC_BPR1_EL1_NS; else return ICC_BPR1_EL1; elsif PSTATE.EL == EL3 then if ICC_SRE_EL3.SRE == ‘0’ then AArch64.SystemAccessTrap(EL3, 0x18); else if SCR_EL3.NS == ‘0’ then return ICC_BPR1_EL1_S; else return ICC_BPR1_EL1_NS;

## _**MSR ICC_BPR1_EL1, <Xt>**_

| **op0** | **op1** | **CRn** | **CRm** | **op2** |

|---|---|---|---|---|

| 0b11 | 0b000 | 0b1100 | 0b1100 | 0b011 |

if PSTATE.EL == EL0 then UNDEFINED; elsif PSTATE.EL == EL1 then if Halted() && HaveEL(EL3) && EDSCR.SDD == ‘1’ && boolean IMPLEMENTATION_DEFINED “EL3 trap priority when SDD == ‘1’” && SCR_EL3.IRQ == ‘1’ then UNDEFINED; elsif ICC_SRE_EL1.SRE == ‘0’ then AArch64.SystemAccessTrap(EL1, 0x18); elsif EL2Enabled() && ICH_HCR_EL2.TALL1 == ‘1’ then AArch64.SystemAccessTrap(EL2, 0x18); elsif EL2Enabled() && HCR_EL2.IMO == ‘1’ then ICV_BPR1_EL1 = X[t]; elsif HaveEL(EL3) && SCR_EL3.IRQ == ‘1’ then if Halted() && EDSCR.SDD == ‘1’ then UNDEFINED; else AArch64.SystemAccessTrap(EL3, 0x18); elsif HaveEL(EL3) then if SCR_EL3.NS == ‘0’ then ICC_BPR1_EL1_S = X[t]; else ICC_BPR1_EL1_NS = X[t]; else ICC_BPR1_EL1 = X[t]; elsif PSTATE.EL == EL2 then if Halted() && HaveEL(EL3) && EDSCR.SDD == ‘1’ && boolean IMPLEMENTATION_DEFINED “EL3 trap priority when SDD == ‘1’” && SCR_EL3.IRQ == ‘1’ then UNDEFINED; elsif ICC_SRE_EL2.SRE == ‘0’ then AArch64.SystemAccessTrap(EL2, 0x18); elsif HaveEL(EL3) && SCR_EL3.IRQ == ‘1’ then if Halted() && EDSCR.SDD == ‘1’ then UNDEFINED; else AArch64.SystemAccessTrap(EL3, 0x18); elsif HaveEL(EL3) then if SCR_EL3.NS == ‘0’ then ICC_BPR1_EL1_S = X[t]; else ICC_BPR1_EL1_NS = X[t]; else ICC_BPR1_EL1 = X[t]; elsif PSTATE.EL == EL3 then if ICC_SRE_EL3.SRE == ‘0’ then AArch64.SystemAccessTrap(EL3, 0x18); else if SCR_EL3.NS == ‘0’ then ICC_BPR1_EL1_S = X[t]; else ICC_BPR1_EL1_NS = X[t];

## 12.3.5 ICV_CTLR_EL1,中断控制器虚拟控制寄存器

ICV_CTLR_EL1的特性:

## 目的

控制GIC虚拟CPU接口行为的各个方面并提供有关实现功能的信息。

## 配置

AArch64系统寄存器ICV_CTLR_EL1的位[31:0]在架构上映射到AArch32系统寄存器ICV_CTLR[31:0]。

## 属性

ICV_CTLR_EL1是一个64位寄存器。

## 字段描述

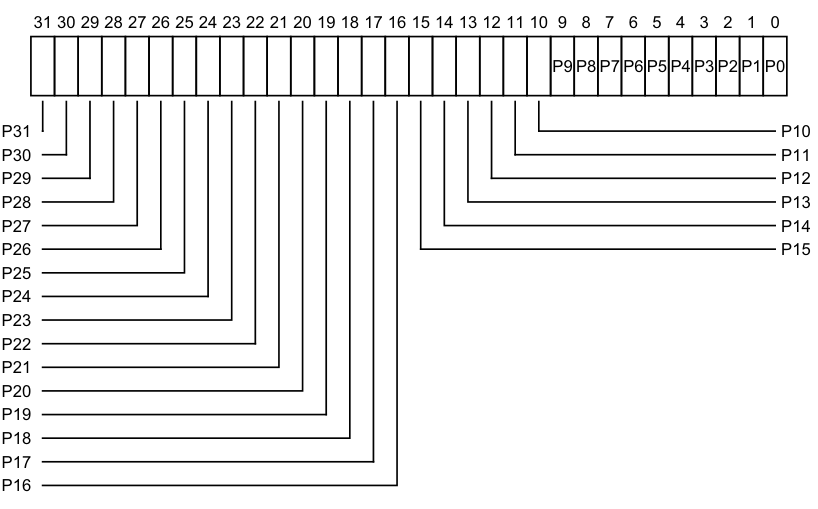

ICV_CTLR_EL1的位分配:

<details><summary>图像文本</summary>

63 20 19 18 17 16 15 14 13 11 10 8 7 2 1 0<br>RES0 IDbits PRIbits RES0<br>ExtRange CBPR<br>RSS EOImode<br>SEIS<br>A3V<br>RES0

</details>

**位[63:20]**

保留,RES0。

## ExtRange,位[19]

扩展INTID范围(只读)。

- 0b0 CPU接口不支持1024..8191范围内的INTID。

- 如果IRI向CPU接口传递1024到8191范围内的中断,行为是UNPREDICTABLE。

> **注意**

Arm强烈建议不要将IRI配置为向不支持它们的PE传递此范围内的中断。

- 0b1 CPU接口支持1024..8191范围内的INTID

- 1024..8191范围内的所有INTID都被视为需要去激活。

ICV_CTLR_EL1.ExtRange是ICC_CTLR_EL1.ExtRange的别名。

## RSS,位[18]

范围选择器支持。可能的值有:

- 0b0 支持亲和性级别0值为0 - 15的目标SGI。

- 0b1 支持亲和性级别0值为0 - 255的目标SGI。

- 此位为只读。

## 位[17:16]

保留,RES0。

## A3V,位[15]

亲和性3有效。只读,写入被忽略。可能的值有:

0b0 虚拟CPU接口逻辑仅支持SGI生成系统寄存器中亲和性3的零值。 0b1 虚拟CPU接口逻辑支持SGI生成系统寄存器中亲和性3的非零值。

## SEIS,位[14]

SEI支持。只读,写入被忽略。指示虚拟CPU接口是否支持本地生成SEI:

0b0 虚拟CPU接口逻辑不支持本地生成SEI。 0b1 虚拟CPU接口逻辑支持本地生成SEI。

## IDbits,位[13:11]

标识符位。只读,写入被忽略。支持的虚拟中断标识符位数:

0b000 16位。 0b001 24位。 所有其他值保留。

## PRIbits,位[10:8]

优先级位。只读,写入被忽略。实现的优先级位数减一。

实现必须实现至少32级虚拟优先级(5个优先级位)。

**注意** 此字段总是返回实现的优先级位数。

组优先级和子优先级之间的分割在二进制点寄存器ICV_BPR0_EL1和ICV_BPR1_EL1中定义。

## 位[7:2]

保留,RES0。

## EOImode,位[1]

虚拟EOI模式。控制写入中断结束寄存器是否也去激活虚拟中断:

0b0 ICV_EOIR0_EL1和ICV_EOIR1_EL1提供优先级下降和中断去激活功能。对ICV_DIR_EL1的访问是UNPREDICTABLE。 0b1 ICV_EOIR0_EL1和ICV_EOIR1_EL1仅提供优先级下降功能。ICV_DIR_EL1提供中断去激活功能。

在热复位时,此字段复位为架构上未知的值。

## CBPR,位[0]

通用二进制点寄存器。控制是否对虚拟0组和虚拟1组中断的中断抢占使用相同的寄存器:

0b0 ICV_BPR1_EL1确定虚拟1组中断的抢占组。 0b1 ICV_BPR1_EL1的读取返回ICV_BPR0_EL1加一,饱和到0b111。对ICV_BPR1_EL1的写入被忽略。

在热复位时,此字段复位为架构上未知的值。

## 访问ICV_CTLR_EL1

访问此寄存器使用系统指令编码空间中的以下编码:

## _**MRS <Xt>, ICC_CTLR_EL1**_

| **op0** | **op1** | **CRn** | **CRm** | **op2** |

|---|---|---|---|---|

| 0b11 | 0b000 | 0b1100 | 0b1100 | 0b100 |